CAN Controllers and Acceptance Filter

164

Philips Semiconductors

Preliminary User Manual

LPC2119/2129/2292/2294

ARM-based Microcontroller

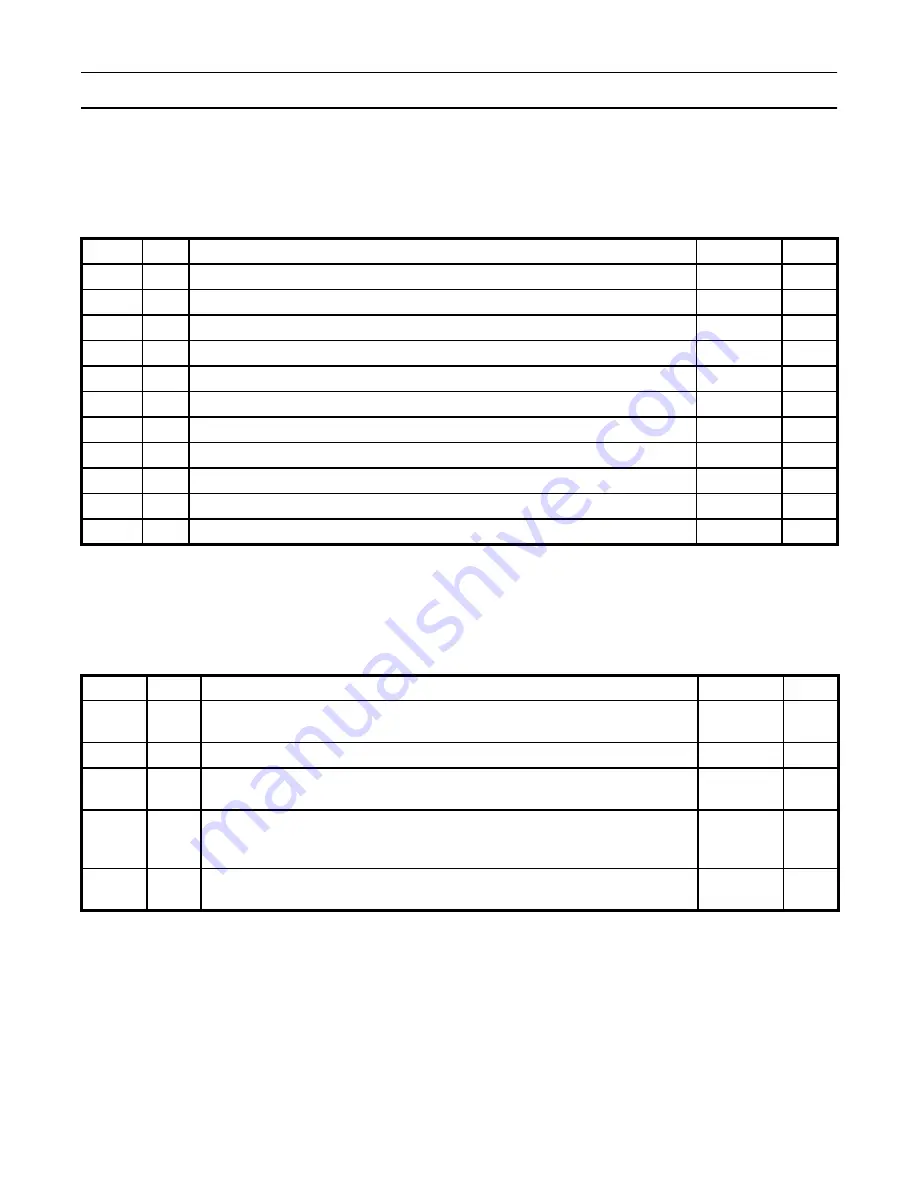

Interrupt Enable Register (CANIER - 0xE00x x010)

This read/write register controls whether various events on the CAN controller will result in an interrupt. Bits 7:0 in this register

correspond 1-to-1 with bits 7:0 in the CANICR register.

Bus Timing Register (CANBTR - 0xE00x x014)

This register controls how various CAN timings are derived from the VPB clock. It can be read at any time, but can only be written

if the RM bit in CANmod is 1.

Table 128: CAN Interrupt Enable Register (CANIER - 0xE00x x010)

CANIER Name Function

Reset Value RM Set

0

RIE

Receiver Interrupt Enable.

0

X

1

TIE1

Transmit Interrupt Enable (1)

0

X

2

EIE

Error Warning Interrupt Enable

0

X

3

DOIE Data Overrun Interrupt Enable

0

X

4

WUIE Wake-Up Interrupt Enable

0

X

5

EPIE Error Passive Interrupt Enable

0

X

6

ALIE

Arbitration Lost Interrupt Enable

0

X

7

BEIE Bus Error Interrupt Enable

0

X

8

IDIE

ID Ready Interrupt Enable

0

X

9

TIE2

Transmit Interrupt Enable (2)

0

X

10

TIE3

Transmit Interrupt Enable (3)

0

X

Table 129: CAN Bus Timing Register (CANBTR - 0xE00x x014)

CANBTR

Name

Function

Reset Value RM Set

0:9

BRP

Baud Rate Prescaler. The VPB clock is divided by (this value plus one) to produce

the CAN clock.

0

X

15:14

SJW

The Synchronization Jump Width is (this value plus one) CAN clocks.

0

X

19:16

TSEG1

The delay from the nominal Sync point to the sample point is (this value plus one)

CAN clocks.

1100

X

22:20

TSEG2

The delay from the sample point to the next nominal sync point is (this value plus

one) CAN clocks. The nominal CAN bit time is (this value plus the value in TSEG1

plus 3) CAN clocks.

001

X

23

SAM

1: the bus is sampled 3 times (recommended for low to medium speed buses)

0: the bus is sampled once (recommended for high speed buses)

0

X