Circuit Descriptions

7.

7.

Circuit Descriptions

Index of this chapter:

7.1 Introduction

7.2 Power Supply

7.3 Power Management

7.4 Circuit Description

Notes:

•

Only new circuits (circuits that are not published recently)

are described.

•

Figures can deviate slightly from the actual situation, due

to different set executions.

•

For a good understanding of the following circuit

descriptions, please use the wiring, block (see chapter

) and circuit diagrams (see chapter

10. Circuit Diagrams and PWB Layouts

).Where necessary,

you will find a separate drawing for clarification.

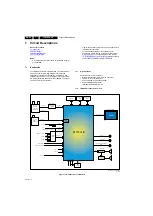

7.1

Introduction

The TPM8.3A LA platform uses MT5301B. It contains decoder

and a TV controller offers high integration for advanced

applications. It combines a transport de-multiplexer, a high

definition video decoder, an audio decoder, a dual-link LVDS/

mini-LVDS transmitter, and an NTST/PAL/SECAM TV decoder

with a 3D comb filter (NTSC/PAL).

7.1.1

Implementation

Key components of this chassis are:

•

MT5301B System-On-Chip (SOC) TV Processor

•

F86WT-17-E Tuner (analogue)

•

STA515W13TR Head Phone amplifier

•

STA339BWTR audio amplifier

•

TMDS361BPAGR HDMI switch

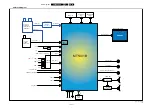

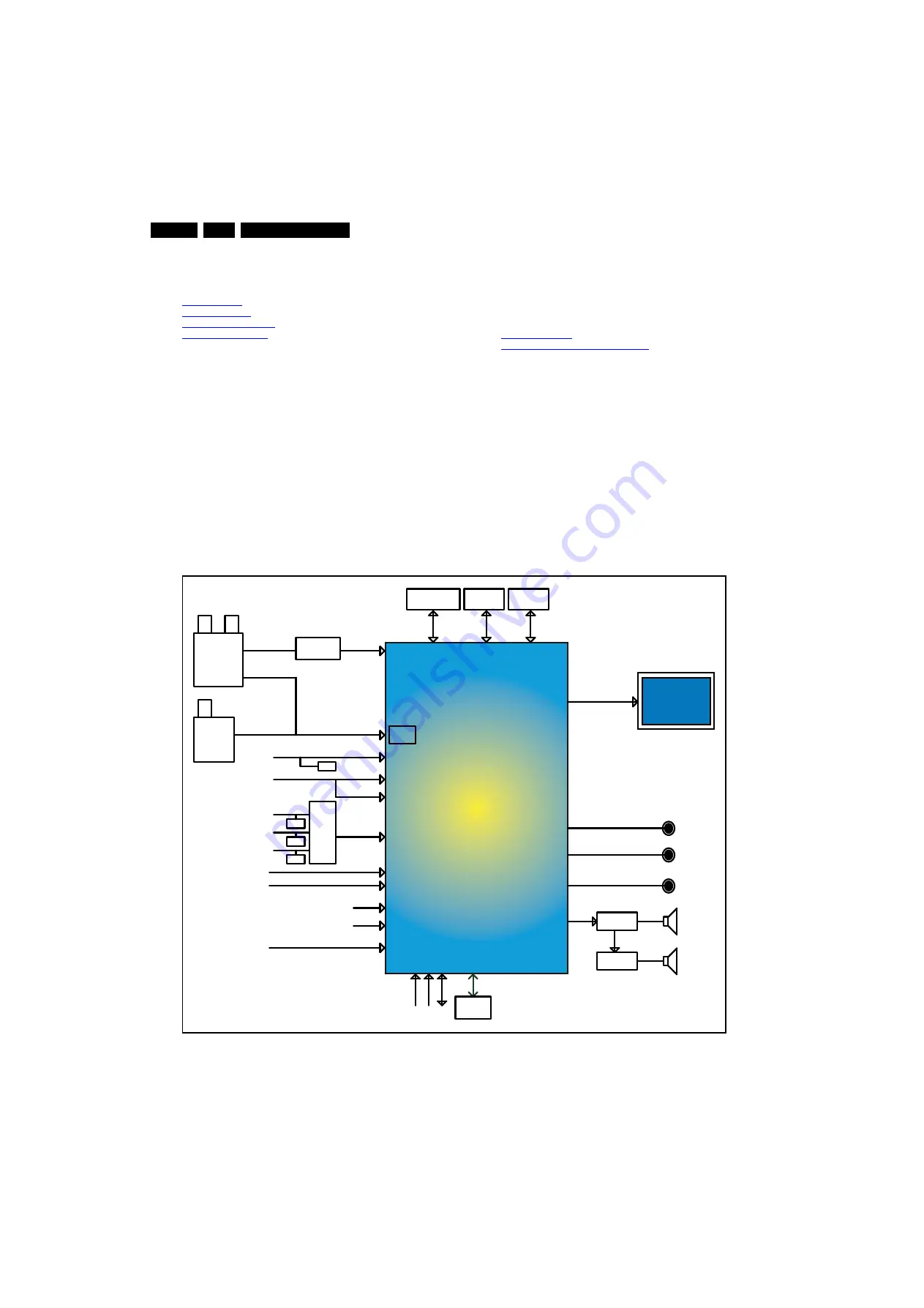

7.1.2

TPM8.3A Architecture Overview

Figure 7-1 Architecture of TPM8.3A LA

19170_205_110704.eps

111006

DDR2 1Gb

I2C

DDC

SPI FLASH

64Mb

NVM

24C32

ATV _RF

TUNER

F86WT-17-E

RC

KEY

UART

24C02

24C02

AUDIO AMP

STA339BWTR

SPK

Digital Audio Output(COIXIAL)

PC IN

DDC

CVI

VIDEO ( By CVI Y connector)

CVBS

YPbPr

RGB

HDMI1

AUDIO IN (PC)

AUDIO R/L (CVI/CVBS)

24C02

24C02

HDMI2

HDMI3

DDC

DDC

TMDS361

BPAGR

SPDIF

I2S

[RX0 : RX3]

NAND FLASH

256Mb

CVBS/AV Out

WOOFER AMP

STA515W

SPK

USB1 2.0

USB1 2.0

ATV

DEMOD

Analog IF+/-

TS (SERIAL)

HDMI 1.3

ATV + DTV

RF TUNER

TDTK-T052D

( RESERVE)

Analog IF+/-

ATBM8848

( RESERVE)

Demodulator

Analog IF+/-

Side AV IN

H/Phone Out

LVDS (50/60 Hz)

LCD PANEL T-CON

MT5301B