Circuit Descriptions, Abbreviation List, and IC Data Sheets

EN 99

LC4.9U AA

9.

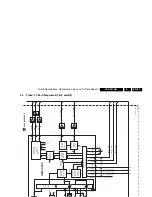

9.11.4 Diagram B12, Type S9993CT (IC7D03, HDMI Panellink), Reserved

Figure 9-11 Internal block diagram and pin configuration

DACVCC

1

100-Pin

TQFP

(Top View)

N/C

2

DACGND

3

N/C

4

DACGNDR

5

DACVCCR

6

AnRPr

7

COMP

8

RSET

9

DACGNDG

10

DACVCCG

11

AnGY

12

DACGNDB

13

DACVCCB

14

AnBPb

15

GND

16

VCC

17

RSVDL

18

RSVDO

19

RSVDO

20

OVCC

21

PGND2

22

PVCC2

23

PLLIN

24

N/C

25

MC

L

K

O

U

T

26

MC

L

K

IN

27

OG

N

D

28

SP

D

IF

29

SD

O

30

WS

31

SC

K

32

HS

Y

N

C

33

V

SYN

C

34

DE

35

Q2

3

36

Q2

2

37

Q2

1

38

Q2

0

39

VC

C

40

GN

D

41

Q1

9

42

Q1

8

43

Q1

7

44

OG

N

D

45

OD

C

K

46

OV

C

C

47

Q1

6

48

Q1

5

49

Q1

4

50

75

Q1

74

OVCC

73

CSDA

72

Q3

71

Q4

70

Q5

69

Q6

68

Q7

67

Q8

66

OGND

65

OVCC

64

Q9

63

Q10

62

Q11

61

Q12

60

Q13

59

58

57

56

55

54

53

52

51

Q0

VC

C

100

GN

D

99

AG

N

D

9

8

R

X

2+

97

R

X

2-

96

AVC

C

9

5

AG

N

D

9

4

AVC

C

9

3

R

X

1+

92

RX

1

-

91

AG

N

D

90

AV

C

C

8

9

AG

N

D

8

8

R

X

0+

87

R

X

0-

86

AG

N

D

85

RX

C+

84

RX

C-

8

3

AVC

C

8

2

EX

T

_

R

E

S

81

P

V

CC1

80

P

G

ND1

79

OG

N

D

7

8

DS

CL

77

DS

DA

76

CSCL

RSVDL

Q2

RESET#

INT

OGND

VCC

GND

SiI 9993

Block Diagram

Pin Configuration

E_14620_149.eps

170305

HDCP

Decryption

Engine

HDCP

Keys

EEPROM

Registers

----------------

Configuration

Logic Block

XOR

Mask

Video

Color

Space

Converter

Up/Down

Sampling

control

signals

I

2

C

Slave

24

DE

Q[23:0]

DSDA

DSCL

R_EXT

RXC±

RX0±

RX1±

RX2±

IN

T

RESET#

Audio

Data

Decode

Logic

Block

SPDIF

MCLKOUT

PanelLink

TMDS

TM

Digital

Core

MCLK

Gen

HSYNC

VSYNC

ODCK

SD0

SCK

WS

MCLKIN

Mode

Control

Aux Data

Logic

Block

control

signals

Video

DAC

30

AnGY

AnRPr

AnBPb

I

2

C

Slave

CSDA

CSCL

OMPC

SETR