Circuit Descriptions, Abbreviation List, and IC Data Sheets

EN 90

LC4.9U AA

9.

9.6.3

Noise Reduction and Noise Estimator

The noise reduction function is a sophisticated successor of the

noise reduction module from the PICNIC-chip, also known as

“LIMERIC”.

Besides the noise reduction part, the Columbus noise

reduction module also comprises a noise estimator. This noise

estimator (the LORE-noise estimator) is a new design with the

ambition of more accuracy and with less control complexity

than the existing noise estimators.

9.7

Video: Scaler Part (Diagram B7, B8 and B9)

The Genesis gm1501 Scaler is a dual channel graphics and

video processing IC for LCD and plasma monitors and

televisions incorporating Picture in Picture, up to SXGA output

resolutions. The Scaler controls the display processing in an

LCD or plasma TV, e.g. like the deflection circuit in a CRT-

based TV. It controls all the view modes (e.g. like "zooming"

and "shifting"). Features like PC (VGA) or HD inputs, are also

handled by this part.

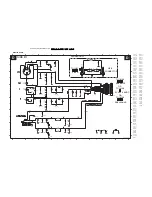

Figure 9-5 Block diagram scaler part

B22

DIGITAL IO

B13

MUX-SYNC INTERFACE

B7

SCALER

B11

FLASH/CONTROL

B10

SDRAM

B18

ADC

B19

COLUMBUS

(Dig. PAL/NTC Comb)

B20

EPLD

B21

EPLD

B12

HDMI

R_SDTV

G_SDTV

B_SDTV

7E01

SC1_R_CVI_Pr_IN

SC1_G_CVI_Y_IN

SC1_B_CVI_Pb_IN

27

3

7

25

1

5

R_PR+

G_Y+

B_PB+

17

14

11

V_PC

2

H_PC

12

7E03

1

13

Vsync_SDTV

Hsync_SDTV

AVSYNC

AHSYNC

15

14

7604

5

1

8

4

L4

L3

ANALOG

INPUT

PORT

DVI/HDMI

INPUT

PORT

7B010

K4D263238F

SDRAM

1Mx32x4

FSDATA

FSADDR

7401

GM1501

GRAPHIC

ZOOM

DISPLAY

TIMING

GEN.

VIDEO

ZOOM

OSD CONTR

OLLER

OUT BLENDER

BRIGHTNESS/CONTRAST/HUE/SA

T

EXTERNAL

ROM

INTERFACE

7C00

MX29LV040QC

FLASH

ROM

512Kx8

OCMDATA

OCMADDR

1P06

1

11

10

12

14

13

15

19

18

20

27

26

28

22

21

23

LVDS_VCC

TXB0-

TXB3+

TXB0+

TXB1-

TXB1+

TXBC+

TXBC-

TXB2-

TXB2+

TXB3-

BINA|Pb

GINA|YINA

RINA|Pr

HOTPLUG

RXC+IN

RXC-IN

FRAME

STORE

CONTROL

MICRO

CONTROLLER

UART

INTERFACE

INTERNAL

RAM

7E02

14

2

11

15

1

12

F624

F625

F626

AE16

AF11

AF16

AF12

AE15

AF15

AE12

AF13

AE14

AF14

D2

C2

B2

Vsync_SDTV

Hsync_SDTV

INTF_Y_OUT

INTF_U_OUT

INTF_V_OUT

19

PC_HD_DET

EF

7L01

EF

7L03

EF

7L02

7L04

MST9883C

A/D

CONV.

COL_Di(1-7)

COL_YA(1-7)

COL_A

COL_D

7M00

T6TU5XBG

COLUMBUS

DIGITAL COMB

FILTER

DRAM

512Kx16x2

7M01

MSM56V16

+2V5_DDR

95

F_15430_062.eps

260705

48

43

54

30

31

56

57

SCL

SDA

COL_Do(1-7)

COL_YB(1-7)

7E00

1

13

3

5

2

12

15

14

4

SD_HD_SEL

10,11

C3

SOG

BINA|Pb

GINA|YINA

RINA|Pr

SC1_CV1_DMMI_R_Pr_IN

SC1_CV1_DMMI_G_Y_IN

SC1_CV1_DMMI_B_Pb_IN

B13

B13

B13

B13

B13

SC1_R_CVI_Pr_IN

SC1_G_CVI_Y_IN

SC1_B_CVI_Pb_IN

B2,B13

B2,B13

B2,B13

B13

B13

B13

B3

B3

B3

B14

B14

B14

B3

B13

B14

B14

B13

B3

B9

SCALER

LVDS

INTERFACE

RECEIVER

7N04

THC63LVDF84B

TXB0-

TXB3+

TXB0+

TXB1-

TXB1+

TXBC+

TXBC-

TXB2-

TXB2+

TXB3-

LVDS

TRANS-

MITTER

7P02

THC63LVDM83R

EPLD

PIXEL+

PROCESSOR

RGB

7N02

EP1C12F256C8N

OR

RGB

4N03

4N13

4N01

4N15

4N07

4N05

4N17

4N19

4N11

4N09

LVDSAp

LVDSAn

LVDSBp

LVDSBn

LVDSCp

LVDSCn

LVDSDp

LVDSDn

LVDSCLKp

LVDSCLKn

LVDSAp

LVDSAn

LVDSBp

LVDSCp

LVDSCn

LVDSDp

LVDSDn

LVDSCLKp

LVDSCLKn

LVDSBn

OR

LVDSA+

LVDSA-

LVDSB+

LVDSB-

LVDSC+

LVDSC-

LVDSD+

LVDSD-

LVDSCLK-

1P07

1

11

12

13

14

15

16

17

18

19

20

24

25

26

21

22

LVDS_VCC

LVDSA+

LVDSA-

LVDSB+

LVDSB-

LVDSC+

LVDSC-

LVDSD+

LVDSD-

LVDSCLK-

T

O

PLASMA P

ANEL

T

O

LCD P

ANEL

Only for sets with

PIXEL PLUS

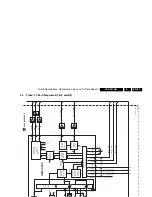

9

9

RGB|CVI_HDA_SEL

HD

PC

Side-AV

EXT2

EXT1

TV

PC_HD_DET H H H H L H

SD_HD_SEL H H H H H H

RGB|CVI_HDA_SEL L H L L L L

SCALER

B7

B7

PC_HD_SEL

I_PC_HD_SEL

R-PR-ADC

G-Y-ADC

B-PB-ADC

B2

B2

B2

1Q03

11

12

5

10

7

8

9

6

4

3

RX0-

RX0+

RXC+

RXC-

RX1-

RX1+

RX2+

RX2-

HDMI/PC-D

1

2

1

2

3

B23

B23

B23

19

1

18

2

1Q01

1

6

10

11

5

15

PC-VGA/

CVI-2

13

14

BINA|Pb

GINA|YINA

RINA|Pr

V_PC

H_PC

5Q01

5Q06

5Q11

5Q21

5Q23

7D03

SII9993CTG100

HDMI

PANELLINK

RECEIVER

HDMI_Y(0-7)

HDMI_CbCr(1-7)

7E05

5

1

8

4

H_HDMI

V_HDMI

33

34

HDMI_VHS

HDMI_VVS

B14

C14