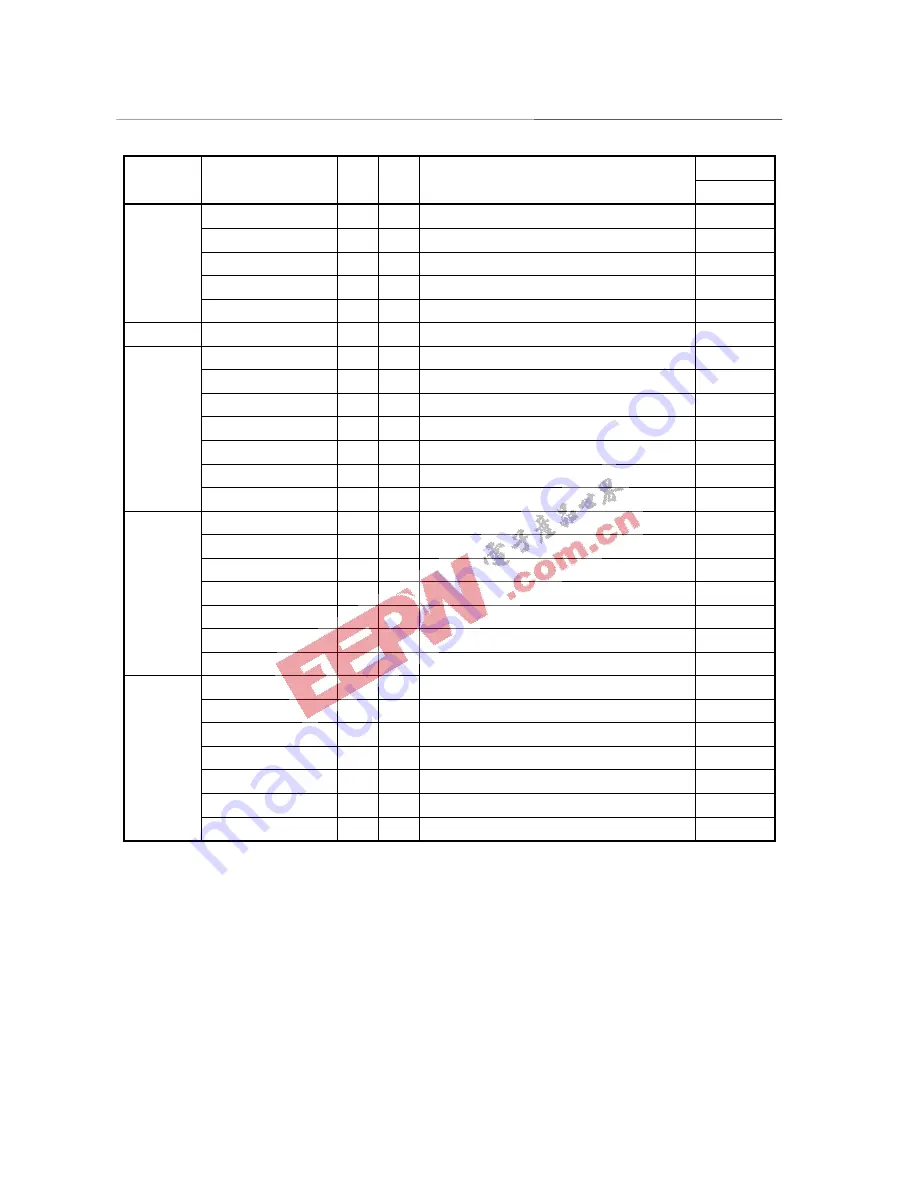

CHAPTER 4 INSTRUCTION SET

User’s Manual U11047EJ3V0UM00

44

Mnemonic

Operand

Byte

Clock

Operation

Flag

Z

AC CY

MOVW

rp, #word

3

6

rp

←

word

AX, saddrp

2

6

AX

←

(saddrp)

saddrp, AX

2

8

(saddrp)

←

AX

AX, rp

Note

1

4

AX

←

rp

rp, AX

Note

1

4

rp

←

AX

XCHW

AX, rp

Note

1

8

AX

↔

rp

ADD

A, #byte

2

4

A, CY

←

A + byte

×

×

×

saddr, #byte

3

6

(saddr), CY

←

(saddr) + byte

×

×

×

A, r

2

4

A, CY

←

A + r

×

×

×

A, saddr

2

4

A, CY

←

A + (saddr)

×

×

×

A, !addr16

3

8

A, CY

←

A + (addr16)

×

×

×

A, [HL]

1

6

A, CY

←

A + (HL)

×

×

×

A, [HL + byte]

2

6

A, CY

←

A + (HL + byte)

×

×

×

ADDC

A, #byte

2

4

A, CY

←

A + byte + CY

×

×

×

saddr, #byte

3

6

(saddr), CY

←

(saddr) + byte + CY

×

×

×

A, r

2

4

A, CY

←

A + r + CY

×

×

×

A, saddr

2

4

A, CY

←

A + (saddr) + CY

×

×

×

A, !addr16

3

8

A, CY

←

A + (addr16) + CY

×

×

×

A, [HL]

1

6

A, CY

←

A + (HL) + CY

×

×

×

A, [HL + byte]

2

6

A, CY

←

A + (HL + byte) + CY

×

×

×

SUB

A, #byte

2

4

A, CY

←

A – byte

×

×

×

saddr, #byte

3

6

(saddr), CY

←

(saddr) – byte

×

×

×

A, r

2

4

A, CY

←

A – r

×

×

×

A, saddr

2

4

A, CY

←

A – (saddr)

×

×

×

A, !addr16

3

8

A, CY

←

A – (addr16)

×

×

×

A, [HL]

1

6

A, CY

←

A – (HL)

×

×

×

A, [HL + byte]

2

6

A, CY

←

A – (HL + byte)

×

×

×

Note Only when rp = BC, DE, or HL.

Remark

One instruction clock cycle is equal to one CPU clock (f

CPU

) cycle selected by the processor clock control

register (PCC).

Summary of Contents for 78K/0S Series

Page 2: ...User s Manual U11047EJ3V0UM00 2 MEMO ...

Page 14: ...User s Manual U11047EJ3V0UM00 14 MEMO ...

Page 28: ...User s Manual U11047EJ3V0UM00 28 MEMO ...

Page 118: ...User s Manual U11047EJ3V0UM00 118 MEMO ...

Page 120: ...User s Manual U11047EJ3V0UM00 120 MEMO ...