© National Instruments

|

2-17

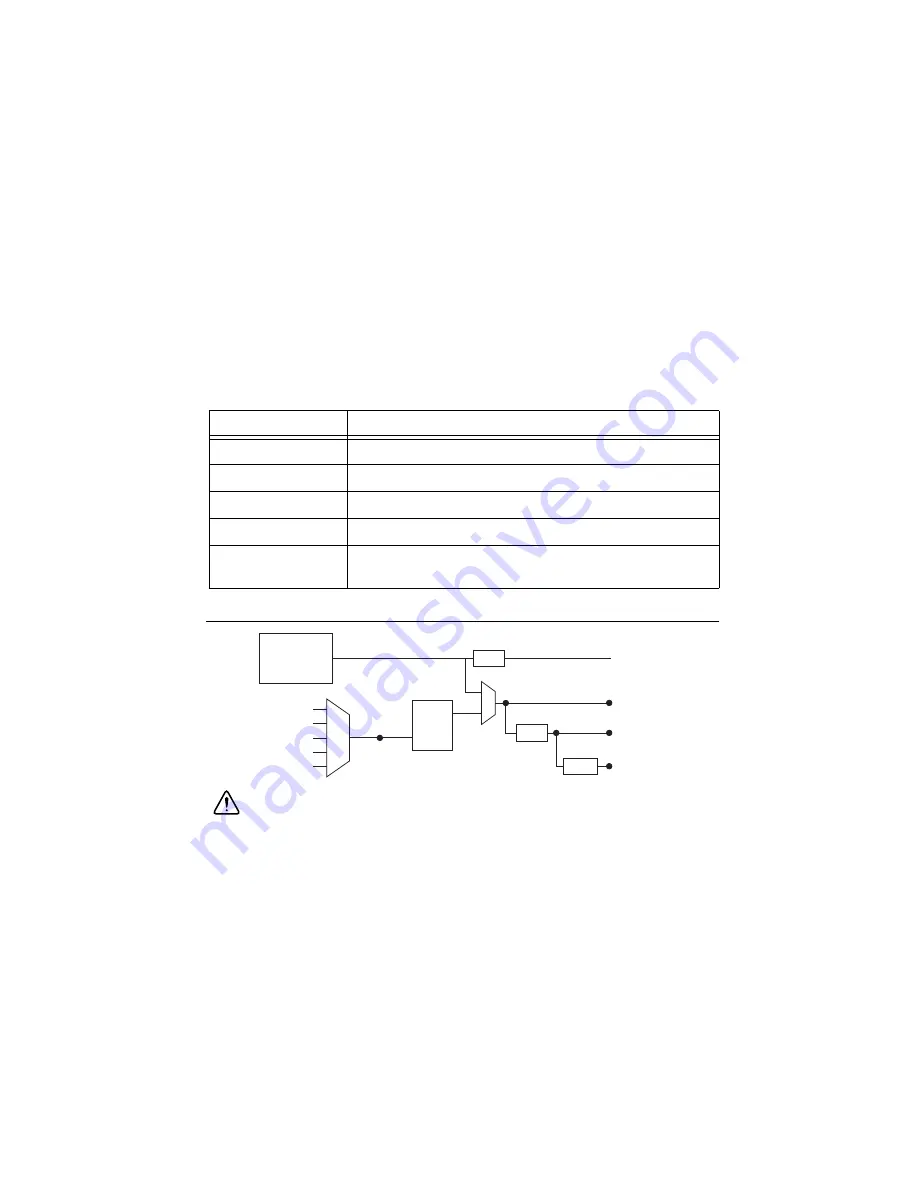

External Reference Clock

An external reference clock can be used as a source for the internal timebase on the

NI PXIe-4300. This clock can be sourced using the signals shown in Table 2-5. Since the clock

is the input of a PLL, it must be 5 MHz, 10 MHz, 20 MHz, or 100 MHz. A PLL locks to the

signal and produces a 100 MHz output, which is then divided down to produce the three

timebases of 100 MHz, 20 MHz and 100 kHz. These timebases can then be used to generate

sample clocks on the device. This circuit also enables the output of a 10 MHz RefClk that can

be routed to PXI_Trig <0..7> and used by another device as its own External Reference Clock

as shown in Figure 2-10.

Figure 2-10.

External Clock Reference

Caution

Do not disconnect an external reference clock once the modules have been

synchronized or are used by a task. Doing so may cause NI-DAQmx to return an

error. Make sure that all tasks using a reference clock are stopped before

disconnecting it.

Table 2-5.

Clock Signal Sourcing

Signal

Description

PXI_Trig<0..7>

Bi-Directional bus connecting each board in the chassis.

PFI<0, 1>

External User Input

PXIe_Clk100

100 MHz clock routed to all slots in the chassis.

PXI_STAR

Point to point route from the System Timing Slot to all other slots.

PXIe_DSTAR<A, B>

Point to point differential routes from the System Timing Slot to

all other slots.

Extern

a

l

Reference

Clock

÷

200

On

b

o

a

rd

100 MHz

O

s

cill

a

tor

PLL

÷

5

÷

10

PXI_Trig <0..7>

PXIe_CLK100

PXI_

S

TAR

PFI<0, 1>

PXIe_D

S

TAR<A,B>

10 MHz RefClk

(To PXI_Trig <0..7>

O

u

tp

u

t

S

elector

s

)

100 MHz

Time

bas

e

20 MHz

Time

bas

e

100 kHz

Time

bas

e