© National Instruments

|

5-7

NI cDAQ-9181/9184/9188/9191 User Manual

The counter counts the number of edges on the Source input while the Gate input remains active.

On each sample clock edge, the counter stores the count in the FIFO of the last pulse width to

complete. The STC3 transfers the sampled values to host memory using a high-speed data

stream.

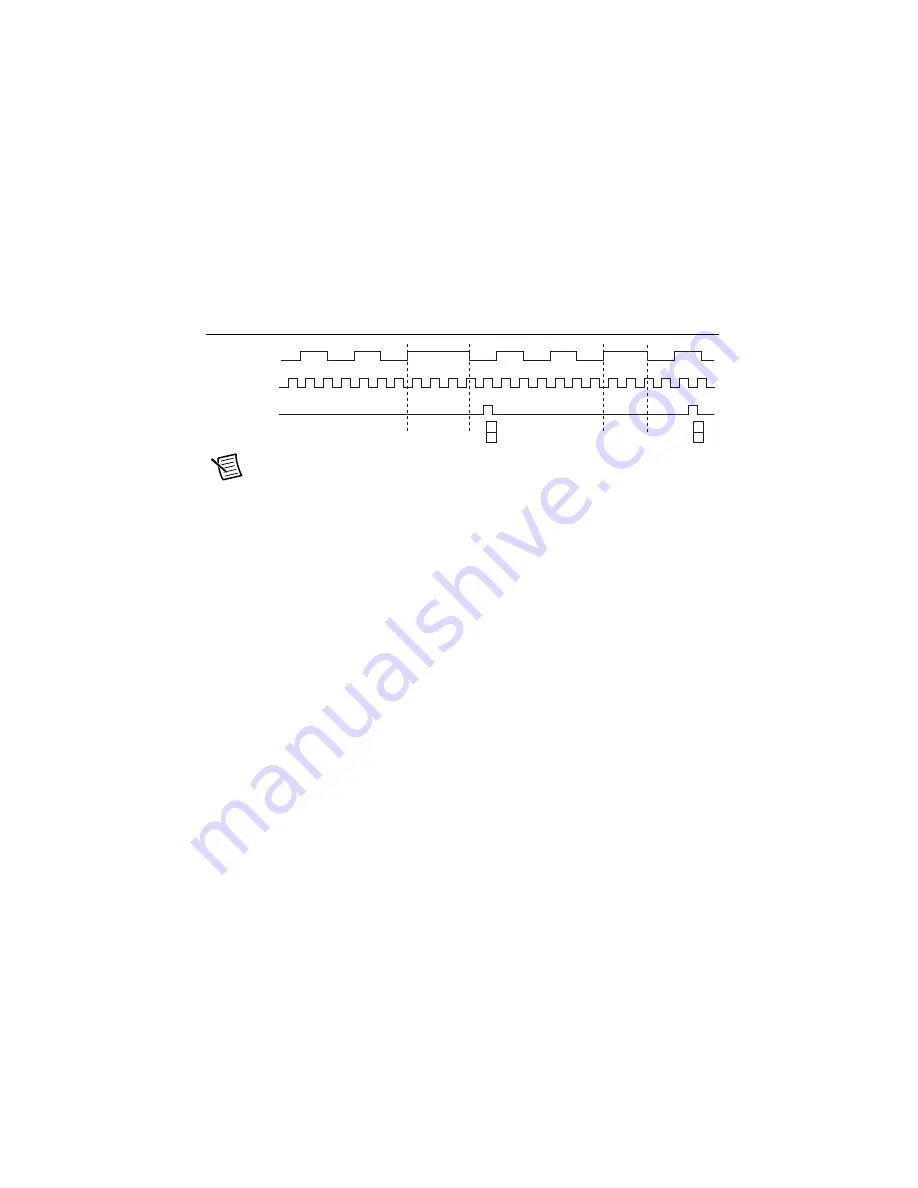

Figure 5-7 shows an example of a sample clocked buffered pulse-width measurement.

Figure 5-7.

Sample Clocked Buffered Pulse-Width Measurement

Note

If a pulse does not occur between sample clocks, an overrun error occurs.

For information about connecting counter signals, refer to the

section.

Pulse Measurement

In pulse measurements, the counter measures the high and low time of a pulse on its Gate input

signal after the counter is armed. A pulse is defined in terms of its high and low time, high and

low ticks or frequency and duty cycle. This is similar to the pulse-width measurement, except

that the inactive pulse is measured as well.

You can route an internal or external periodic clock signal (with a known period) to the Source

input of the counter. The counter counts the number of rising (or falling) edges occurring on the

Source input between two edges of the Gate signal.

You can calculate the high and low time of the Gate input by multiplying the period of the Source

signal by the number of edges returned by the counter.

Refer to the following sections for more information about cDAQ chassis pulse measurement

options:

•

•

Implicit Buffered Pulse Measurement

•

Sample Clocked Buffered Pulse Measurement

P

u

l

s

e

S

o

u

rce

Sa

mple Clock

2

3

4

2

4

3

2

2

4

B

u

ffer