8224 N/B Maintenance

8224 N/B Maintenance

91

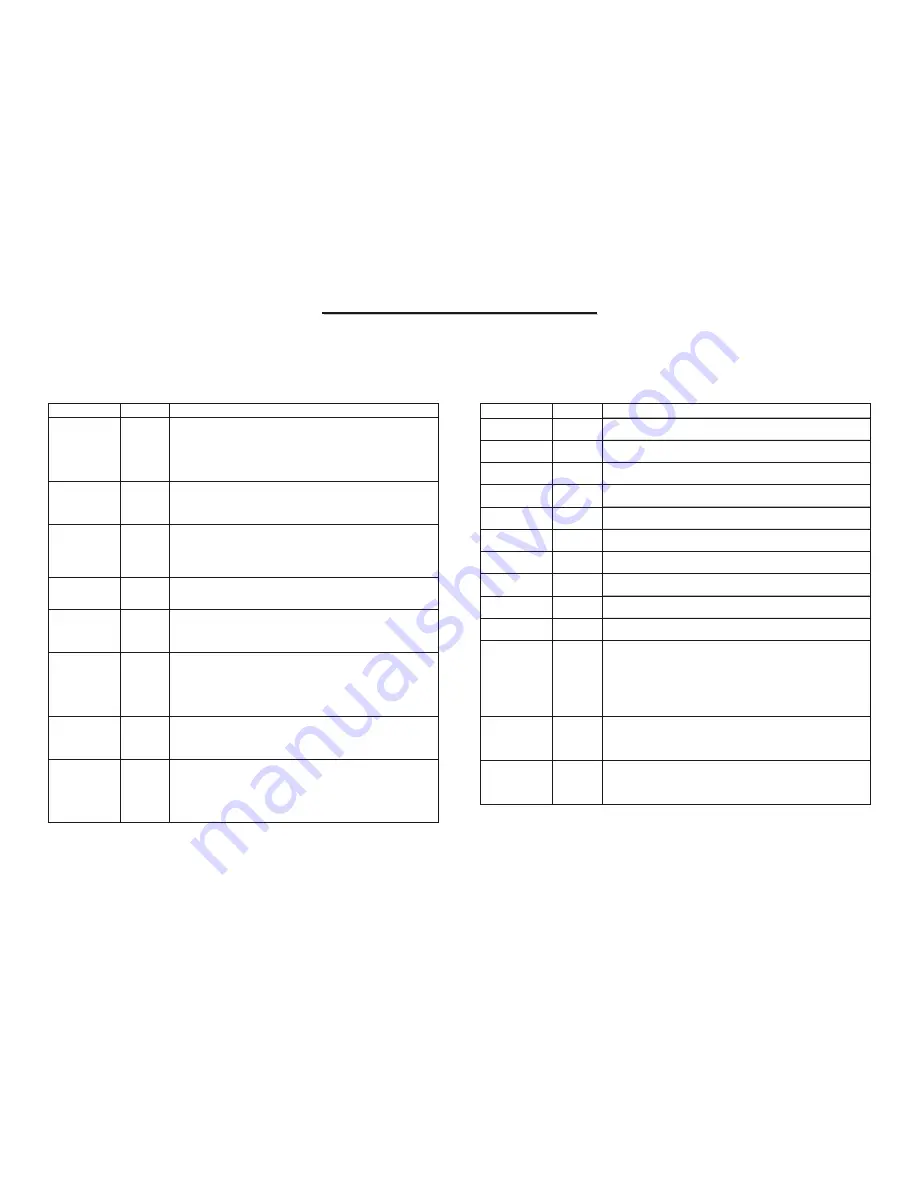

5.2 Intel ICH7-M South Bridge (2)

PCI Interface Signals (Continued)

Signal Name

Type

Description

PERR#

I/O

Parity Error:

An external PCI device drives PERR# when it receives data that has a

parity error. The ICH7 drives PERR# when it detects a parity error.

The ICH7 can either generate an NMI# or SMI# upon detecting a

parity error (either detected internally or reported via the PERR#

signal).

REQ[0:3]#

REQ[4]#/

GPIO22

REQ[5]#/

GPIO1

I

PCI Requests:

The ICH7 supports up to 6 masters on the PCI bus. The REQ[4]# and

REQ5# pins can instead be used as a GPIO.

GNT[0:3]#

GNT[4]#/

GPIO48

GNT[5]#/

GPIO17#

O

PCI Grants:

The ICH7 supports up to 6 masters on the PCI bus. The GNT4# and

GNT5# pins can instead be used as a GPIO. Pull-up resistors are not

required on these signals. If pull-ups are used, they should be tied to

the Vcc3_3 power rail. GNT5#/GPIO17 has an internal pull-up.

PCICLK

I

NOTE: PCI Clock:

This is a 33 MHz clock. PCICLK provides timing for all transactions

on the PCI Bus.

PCIRST#

O

PCI Reset:

This is the Secondary PCI Bus reset signal. It is a logical OR of the

primary interface PLTRST# signal and the state of the Secondary Bus

Reset bit of the Bridge Control register (D30:F0:3Eh, bit 6).

PLOCK#

I/O

PCI Lock:

This signal indicates an exclusive bus operation and may require

multiple transactions to complete. The ICH7 asserts PLOCK# when it

performs non-exclusive transactions on the PCI bus. PLOCK# is

ignored when PCI masters are granted the bus in desktop

configurations.

SERR#

I/OD

System Error:

SERR# can be pulsed active by any PCI device that detects a system

error condition. Upon sampling SERR# active, the ICH7 has the

ability to generate an NMI, SMI#, or interrupt.

PME#

I/OD

PCI Power Management Event:

PCI peripherals drive PME# to wake the system from low-power

states S1–S5. PME# assertion can also be enabled to generate an SCI

from the S0 state. In some cases the ICH7 may drive PME# active

due to an internal wake event. The ICH7 will not drive PME# high,

but it will be pulled up to VccSus3_3 by an internal pull-up resistor.

Serial ATA Interface Signals

Name Type

Description

SATA0TXP

SATA0TXN

O

Serial ATA 0 Differential Transmit Pair:

These are outbound high-speed differential signals to Port 0.

SATA0RXP

SATA0RXN

I

Serial ATA 0 Differential Receive Pair:

These are inbound high-speed differential signals from Port 0.

SATA1TXP

SATA1TXN

O

Serial ATA 1 Differential Transmit Pair:

These are outbound high-speed differential signals to Port 1.

SATA1RXP

SATA1RXN

I

Serial ATA 1 Differential Receive Pair:

These are inbound high-speed differential signals from Port 1.

SATA2TXP

SATA2TXN

O

Serial ATA 2 Differential Transmit Pair:

These are outbound high-speed differential signals to Port 2.

SATA2RXP

SATA2RXN

I

Serial ATA 2 Differential Receive Pair:

These are inbound high-speed differential signals from Port 2.

SATA3TXP

SATA3TXN

O

Serial ATA 3 Differential Transmit Pair:

These are outbound high-speed differential signals to Port 3.

SATA3RXP

SATA3RXN

I

Serial ATA 3 Differential Receive Pair:

These are inbound high-speed differential signals from Port 3.

SATARBIAS

O

Serial ATA Resistor Bias:

These are analog connection points for an external resistor to ground.

SATARBIAS#

I

Serial ATA Resistor Bias Complement:

These are analog connection points for an external resistor to ground.

SATA0GP/

GPIO21

I

Serial ATA 0 General Purpose:

This is an input pin which can be configured as an interlock switch

corresponding to SATA Port 0. When used as an interlock switch

status indication, this signal should be drive to ‘0’ to indicate that the

switch is closed and to ‘1’ to indicate that the switch is open.

If interlock switches are not required, this pin can be configured as

GPIO21.

SATA1GP/

GPIO19

I

Serial ATA 1 General Purpose:

Same function as SATA0GP, except for SATA Port 1.

If interlock switches are not required, this pin can be configured as

GPIO19.

SATA2GP/

GPIO36

I

Serial ATA 2 General Purpose:

Same function as SATA0GP, except for SATA Port 2.

If interlock switches are not required, this pin can be configured as

GPIO36.

MiTac Secret

Confidential Document

Summary of Contents for 8224

Page 164: ...M iTacSecret ConfidentialDocum ent...

Page 165: ...M iTacSecret ConfidentialDocum ent...