The V

DD

sense connection draws very little current from the target processor. The actual power comes from the

MPLAB PICkit 4 In-Circuit Debugger system, as the V

DD

sense line is used as a reference only to track the target

voltage.

The clock and data connections are interfaces with the following characteristics:

• Clock and data signals are in high-impedance mode (even when no power is applied to the MPLAB PICkit 4 In-

Circuit Debugger system).

• Clock and data signals are protected from high voltages caused by faulty target systems, or improper

connections.

• Clock and data signals are protected from high current caused from electrical shorts in faulty target systems.

Table 11-4. Electrical Logic Table

Logic Inputs

V

IH

= V

DD

x 0.7V (min.)

V

IL

= V

DD

x 0.3V (max.)

Logic Outputs

V

DD

= 5V

V

DD

= 3V

V

DD

= 2.3V

V

DD

= 1.4V

V

OH

= 3.8V min.

V

OH

= 2.4V min.

V

OH

= 1.9V min.

V

OH

= 1.0V min.

V

OL

= 0.55V max.

V

OL

= 0.55V max.

V

OL

= 0.3V max.

V

OL

= 0.1V max.

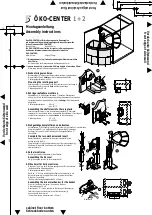

Figure 11-2. MPLAB

®

PICkit

™

4 Debugger Connector Pinout

Hardware Specification

©

2020 Microchip Technology Inc.

User Guide

DS50002751D-page 59