DS3232

Power Control

This function is provided by a temperature-compensat-

ed voltage reference and a comparator circuit that

monitors the V

CC

level. When V

CC

is greater than V

PF

,

the part is powered by V

CC

. When V

CC

is less than V

PF

but greater than V

BAT

, the DS3232 is powered by V

CC

.

If V

CC

is less than V

PF

and is less than V

BAT

, the

device is powered by V

BAT

. See Table 1.

To preserve the battery, the first time V

BAT

is applied to

the device, the oscillator does not start up and no tem-

perature conversions take place until V

CC

exceeds V

PF

or until a valid I

2

C address is written to the part. After

the first time V

CC

is ramped up, the oscillator starts up

and the V

BAT

source powers the oscillator during

power-down and keeps the oscillator running. When

the DS3232 switches to V

BAT

, the oscillator may be dis-

abled by setting the

EOSC

bit.

V

BAT

Operation

There are several modes of operation that affect the

amount of V

BAT

current that is drawn. While the device

is powered by V

BAT

and the serial interface is active,

active battery current, I

BATA

, is drawn. When the serial

interface is inactive, timekeeping current (I

BATT

), which

includes the averaged temperature conversion current,

I

BATTC

, is used (refer to Application Note 3644:

Power

Considerations for Accurate Real-Time Clocks for

details). Temperature conversion current, I

BATTC

, is

specified since the system must be able to support the

periodic higher current pulse and still maintain a valid

voltage level. Data retention current, I

BATTDR

, is the

current drawn by the part when the oscillator is

stopped (

EOSC

= 1). This mode can be used to mini-

mize battery requirements for times when maintaining

time and date information is not necessary, e.g., while

the end system is waiting to be shipped to a customer.

Pushbutton Reset Function

The DS3232 provides for a pushbutton switch to be con-

nected to the

RST

output pin. When the DS3232 is not in

a reset cycle, it continuously monitors the

RST

signal for a

low going edge. If an edge transition is detected, the

DS3232 debounces the switch by pulling the

RST

low.

After the internal timer has expired (PB

DB

), the DS3232

continues to monitor the

RST

line. If the line is still low, the

DS3232 continuously monitors the line looking for a rising

edge. Upon detecting release, the DS3232 forces the

RST

pin low and holds it low for t

RST

.

The same pin,

RST

, is used to indicate a power-fail con-

dition. When V

CC

is lower than V

PF

, an internal power-

fail signal is generated, which forces the

RST

pin low.

When V

CC

returns to a level above V

PF

, the

RST

pin is

held low for t

REC

to allow the power supply to stabilize.

If the oscillator is not running (see the

Power Control

section) when V

CC

is applied, t

REC

is bypassed and

RST

immediately goes high.

Assertion of the

RST

output, whether by pushbutton or

power-fail detection, does not affect the internal opera-

tion of the DS3232.

Real-Time Clock

With the clock source from the TCXO, the RTC provides

seconds, minutes, hours, day, date, month, and year

information. The date at the end of the month is automati-

cally adjusted for months with fewer than 31 days, includ-

ing corrections for leap year. The clock operates in either

the 24-hour or 12-hour format with an

AM

/PM indicator.

The clock provides two programmable time-of-day

alarms and a programmable square-wave output. The

INT

/SQW pin either generates an interrupt due to alarm

condition or outputs a square-wave signal and the

selection is controlled by the bit INTCN.

SRAM

The DS3232 provides 236 bytes of general-purpose

battery-backed read/write memory. The I

2

C address

ranges from 14h to 0FFh. The SRAM can be written or

read whenever V

CC

or V

BAT

is greater than the mini-

mum operating voltage.

Address Map

Figure 1 shows the address map for the DS3232 time-

keeping registers. During a multibyte access, when the

address pointer reaches the end of the register space

(0FFh), it wraps around to location 00h. On an I

2

C

START or address pointer incrementing to location 00h,

the current time is transferred to a second set of regis-

ters. The time information is read from these secondary

registers, while the clock may continue to run. This

eliminates the need to reread the registers in case the

main registers update during a read.

I

2

C Interface

The I

2

C interface is accessible whenever either V

CC

or

V

BAT

is at a valid level. If a microcontroller connected to

the DS3232 resets because of a loss of V

CC

or other

Extremely Accurate I

2

C RTC with

Integrated Crystal and SRAM

10

____________________________________________________________________

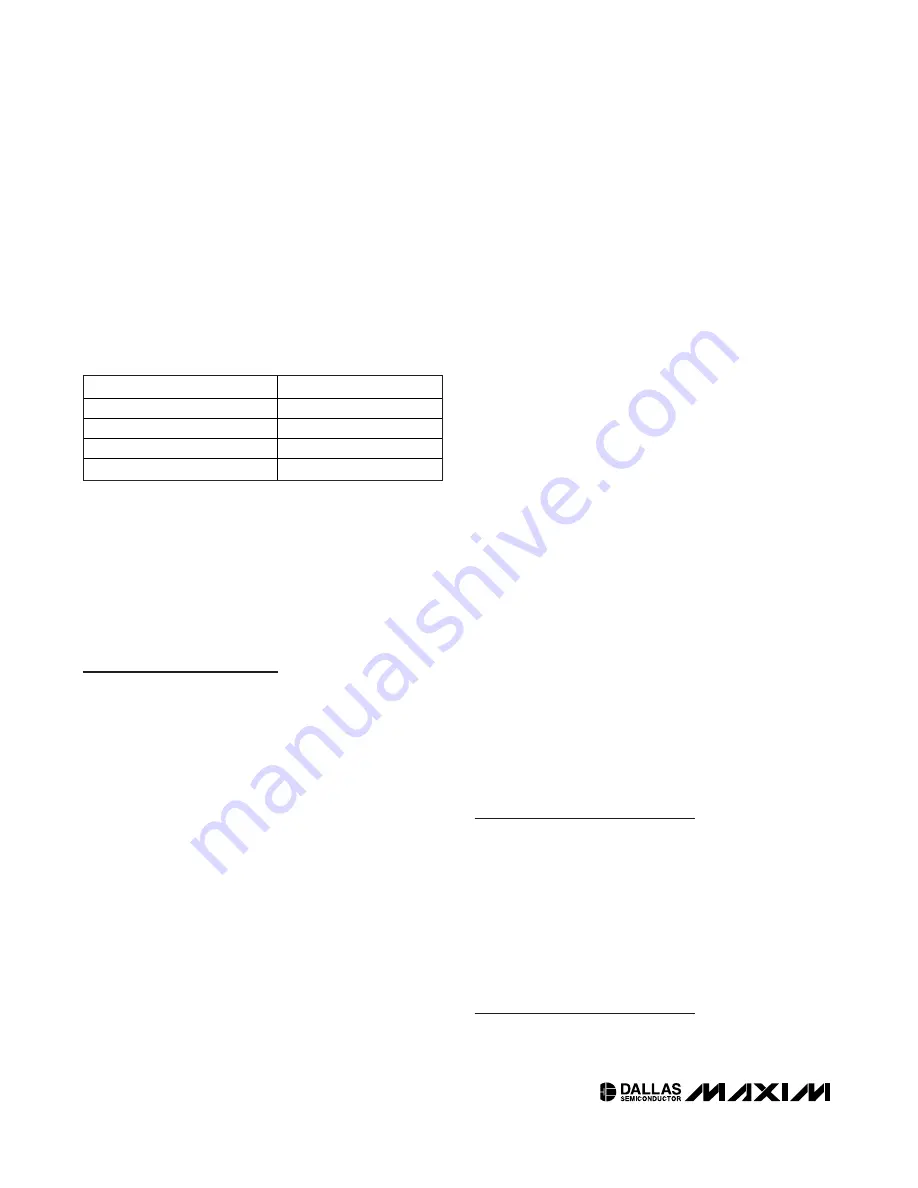

SUPPLY CONDITION

POWERED BY

V

CC

< V

PF

, V

CC

< V

BAT

V

BAT

V

CC

< V

PF

, V

CC

> V

BAT

V

CC

V

CC

> V

PF

, V

CC

< V

BAT

V

CC

V

CC

> V

PF

, V

CC

> V

BAT

V

CC

Table 1. Power Control