Group 2 General-Purpose Registers

4-5

MSIZE

Symbol Size

R/W [2:0]

This value indicates the size of symbols:

0b000 = 1 bit

0b001 = 2 bit

0b010 = 3 bit

0b011 = 4 bit

0b100 = 5 bit

0b101 = 6 bit

0b110 = 7 bit

0b111 = 8 bit.

The reset value is 0b101

4.1.3 Register 2

RES

Reserved

7

This bit is reserved.

FDEL

FIFO Delay

R/W [6:0]

This parameter indicates the FIFO delay value in the

Gray Code. Writing to this location loads the ICLK

address counter with 0 and the OCLK-driven address

counter to the FDEL value. If the FIFO is automatically

reset, the L64777 also uses this value for the

OCLK-driven address. The reset value is 0b110 0000.

4.1.4 Register 3

SMAG

Sign Magnitude

R/W 7

When this bit is 0, the L64777 outputs a two’s

complement at the Nyquist filter. When this bit is 1, the

L64777 inverts the sign bit and the output sign magnitude

representation. The reset value is 0.

RES

Reserved

6, 4, 0

These bits are reserved.

7

6

0

RES

FDEL

7

6

5

4

3

2

1

0

SMAG

RES

IQ_EX

RES

SCR_OFF

RS_OFF

INT_OFF

RES

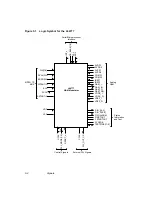

Summary of Contents for L64777

Page 1: ...L64777 DVB QAM Modulator Order Number I14031 A Technical Manual June 2000...

Page 10: ...x Contents...

Page 14: ...1 4 Introduction...

Page 90: ...5 10 Signals...

Page 110: ...A 8 Programming the L64777 in Serial Host Interface Mode...

Page 116: ...C 2 Monitoring Device Internal Signals...

Page 124: ......