Sync/EF Reinsertion Unit

2-19

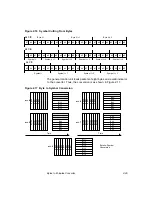

Figure 2.11 Scrambler Basic Serial Architecture

The scrambler block consists of two major modules: one to generate a

pseudo-random binary sequence (PRBS) that modifies the incoming

data stream, and the other a control module that properly aligns data

with the PRBS.

The PRBS the descrambler module produces is characterized by the

following generator polynomial:

For initialization, choose a specific value for the 15-tap shift register (see

Figure 2.12).

Figure 2.12 Shift Register Initialization Sequence

The L64777 uses a special sync word (0xB8), generated by inverting

every eighth transport sync word (0x47), to align the descrambler with

the incoming data stream. The L64777 applies the first bit of the PRBS

to the first data bit following the inverted sync byte and freezes the

scrambler register contents during gaps for RS check words. During the

following noninverted sync words, the descrambler sequence generator

is kept in operation but does not modify the data stream. The L64777

resets the descrambler sequence after every inverted sync word. The

Scrambled

Bitstream

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Shift Register

Bitstream

XOR

XOR

Shift_Enable

Initial Load

&

Control

1

x

14

x

15

+

+

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

1

0

0

1

0

1

0

1

0

0

0

0

0

0

0

Summary of Contents for L64777

Page 1: ...L64777 DVB QAM Modulator Order Number I14031 A Technical Manual June 2000...

Page 10: ...x Contents...

Page 14: ...1 4 Introduction...

Page 90: ...5 10 Signals...

Page 110: ...A 8 Programming the L64777 in Serial Host Interface Mode...

Page 116: ...C 2 Monitoring Device Internal Signals...

Page 124: ......