LTC1760

32

1760fc

For more information

www.linear.com/LTC1760

SMBALERT

is used to monitor charging status of Battery 1.

Allowed values are:

Low: Battery 1 is charging.

High: Battery 1 not charging (AC is not present or bat-

tery is not present).

Blinking: Battery 1 charge complete (AC is present,

battery is present and not charging).

SCL is an input and is used to determine the blinking rate

of SDA and

SMBALERT

. Tie SCL high if blinking is not

desired. This will provide two different states to indicate

charging (output low) and not charging (output high).

6.2 Hardware Charge Inhibit

When MODE is tied to GND and V

VDDS

>V

IH_VDDS

, charging

is inhibited and BatterySystemStateCont(CHARGING_INHIBIT)

will report a logic high.

6.3 Charging When SCL And SDA Are Low

When MODE is tied to V

CC2

and V

VDDS

< V

IL_VDDS

, SDA

and SCL are not used and will not interfere with LTC1760

battery communication. This feature allows the LTC1760 to

autonomously charge when SCL and SDA are not available.

This scenario might occur when SMBus Host has powered

down and is no longer pulling up on SCL and SDA.

6.4 Charging With an SMBus Host

When Mode is tied to V

CC2

and V

VDDS

> V

IH_VDDS

, SDA

and SCL are used to communicate with the SMBus Host.

7 Battery Charger Controller

The LTC1760 charger controller uses a constant off-time,

current mode step-down architecture. During normal

operation, the top MOSFET is turned on each cycle when

the oscillator sets the SR latch and turned off when the

main current comparator I

CMP

resets the SR latch. While

the top MOSFET is off, the bottom MOSFET is turned on

until either the inductor current trips the current compara-

tor I

REV

, or the beginning of the next cycle. The oscillator

uses the equation:

t

OFF

= (V

DCIN

- V

BAT

)/(V

DCIN

• f

OSC

)

OPERATION

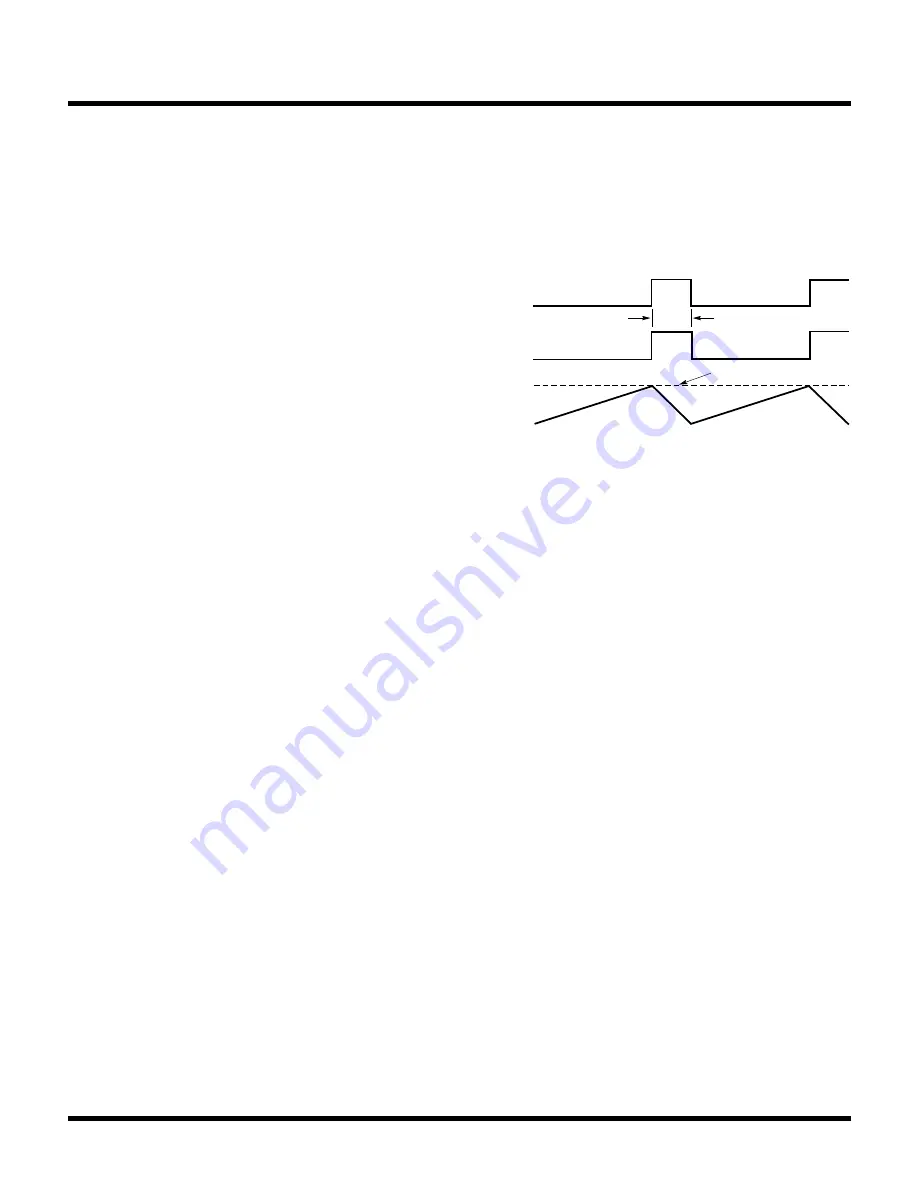

TGATE

BGATE

ON

ON

OFF

OFF

t

OFF

TRIP POINT SET BY I

TH

VOLTAGE

INDUCTOR

CURRENT

1760 F04

Figure 4.

to set the bottom MOSFET on time. The result is quasi-

constant frequency operation where the converter fre-

quency remains nearly constant over a wide range of

output voltages. This activity is diagrammed in Figure 4.

The peak inductor current, at which I

CMP

resets the SR

latch, is controlled by the voltage on I

TH

. I

TH

is in turn

controlled by several loops, depending upon the situation

at hand. The average current control loop converts the

voltage between CSP and BAT to a representative current.

Error amp CA2 compares this current against the desired

current programmed by the I

DAC

at the I

SET

pin and adjusts

I

TH

for the desired voltage across R

SENSE

.

The voltage at BAT is divided down by an internal resis-

tor divider set by the V

DAC

and is used by error amp EA

to decrease I

TH

if the divider voltage is above the 0.8V

reference.

The amplifier CL1 monitors and limits the input current,

normally from the AC adapter, to a preset level (100 mV/

R

CL

). At input current limit, CL1 will decrease the I

TH

volt-

age and thus reduce battery charging current.

An over-voltage comparator, OV, guards against transient

overshoots (>7.5%). In this case, the top MOSFET is turned

off until the over-voltage condition is cleared. This feature

is useful for batteries which “load dump” themselves by

opening their protection switch to perform functions such

as calibration or pulse-mode charging.

The top MOSFET driver is powered from a floating boot-

strap capacitor C4. This capacitor is normally recharged

from V

CC

through an external diode when the top MOS-

FET is turned off. As V

IN

decreases towards the selected