A

A

B

B

C

C

D

D

E

E

4

4

3

3

2

2

1

1

CHROMA

CHROMA

LUMA

LUMA

CVBS

CVBS

BAIN_B

RAIN_B

VSYNC_ B

VSYNC_ B

GAIN_B

SDA

SCL

RESETn

RESETn

RX1-

RX1-

RX2+

RX2+

RX2-

RX2-

A

V

D

D

SCL

HSYNC_B

HSYNC_B

RX1+

RX1+

RX0-

RX0-

RX0+

RX0+

RXC-

RXC-

RXC+

RXC+

RAIN_B

GAIN_B

BAIN_B

SCL

D[0:7]

P

O

W

E

R

O

N

SDA

D

[0

:7

]

VUV[7:0]

VUV[7:0]

AUDIO_VOL

A

U

D

IO

_

V

O

L

GCLK

GCLK

GGE[7:0]

GGE[7:0]

CS1n

CS1n

SCL

VVS

VVS

VFIELD

VFIELD

FAN_P

R

E

S

E

T

KEY9

KEY9

R

O

M

W

E

n

DBE[7:0]

D

C

K

E

X

T

GVS

GVS

GRE[7:0]

GRE[7:0]

VPEN

VPEN

VHS

VHS

SCL

B

H

E

N

n

M

C

K

E

X

T

R

X

D

GFBK

GFBK

VCLK

VCLK

LAMP_P

SDA

IR

R

C

V

R

CS0n

CS0n

DVS

POWERON

TXD

R

O

M

O

E

n

GBE[7:0]

GBE[7:0]

VY[7 :0]

VY[7 :0]

AUDIO_MUT

A

U

D

IO

_

M

U

T

D EN

A

0

DCLK

T

X

D

GHS

GHS

SDA

SDA

IRR CVR

GPENSOG

GPENSOG

D HS

K

E

Y

S

T

O

N

E

LAMPLITZ

V

P

P

E

N

RESETZ

DGE[7:0]

DRE[7:0]

D

[0

:1

5

]

RXD

A

[1

9

:1

]

3.3V

VDD

SCL

SDA

GND

POWERON

DEN

RESETZ

LAMPLITZ

DGE[7:0]

DHS

DRE[7:0]

DCLK

DVS

DBE[7:0]

LAMP_P

FAN_P

VDD

3.3V

VDD

VDD

3.3V

VDD

3.3V

VDD

3.3V

VDD

V33

V33

VDD

Note: To DDP1000 input port

Note: Lamp on/off detect signal.

Reject RC1 and RC2 the front end I2C bus

would be separated with DDP1000.

Economy mode switch.

PW166

015_PW166

VCLK

VFIELD

VVS

VHS

VPEN

VY[7:0]

GGE[7:0]

GRE[7:0]

GVS

GBLKSPL

GHS

GFBK

GCLK

GBE[7:0]

GCOAST

T

D

O

T

X

D

R

O

M

W

E

n

T

C

K

R

X

D

M

C

K

E

X

T

R

O

M

O

E

n

IR

R

C

V

R

T

M

S

A

[1

9

:1

]

D

C

K

E

X

T

R

E

S

E

T

D

[0

:1

5

]

SDA

DVS

DHS

DRE[7:0]

DCLK

DGE[7:0]

DBE[7:0]

A

0

B

H

E

N

n

DEN

VUV[7:0]

POWERON

RESETZ

DRO[7:0]

DGO[7:0]

DBO[7:0]

SCL

V

P

P

E

N

A

U

D

IO

_

M

U

T

3.3V

CS0n

LAMPLITZ

GND

LAMP_P

K

E

Y

S

T

O

N

E

A

U

D

IO

_

V

O

L

CS1n

FAN_P

VDD

PC_SW

D

[0

:7

]

GPENSOG

KEY9

KEY

017_KEY

D[0:7]

CS0n

VDD

3.3V

GND

CS1n

RESETn

KEY9

MISC

016_MISC

P

O

W

E

R

O

N

D

C

K

E

X

T

M

C

K

E

X

T

VDD

3.3V

GND

K

E

Y

S

T

O

N

E

S

D

A

S

C

L

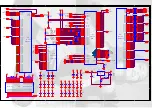

INPUT

011_INPUT

LUMA

CHROMA

CVBS

BAIN_B

GAIN_B

VSYNC_B

HSYNC_B

RAIN_B

VDD

G

N

D

RXD

TXD

IRRCVR

AUDIO_VOL

AUDIO_MUT

RX1+

RX1-

RX2+

RX2-

RX0+

RX0-

RXC-

RXC+

DECODE

012_DECODE

CVBS

LUMA

CHROMA

SCL

SDA

VUV[7:0]

VY[7:0]

VVS

VFILD

VPEN

VHS

VCLK

VDD

GND

V33

L

L

C

1

L

L

C

2

RAIN_B

GAIN_B

BAIN_B

A

V

D

D

AFE

013_AFE

SCL

SDA

HSYNC_B

VSYNC_B

GBE[7:0]

GGE[7:0]

GRE[7:0]

GFBK

GHS

GVS

GCLK

BAIN_B

GAIN_B

RAIN_B

V33

VDD

GND

RX1+

RX1-

RX2+

RX2-

A

V

D

D

RX0+

RX0-

RXC+

RXC-

GPENSOG

MEMORY&KEYSTONE

014_MEMORY&KEYSTONE

V

P

P

E

N

A

[1

9

:1

]

D

[0

:1

5

]

3.3V

GND

R

O

M

W

E

n

R

O

M

O

E

n

SCL

SDA

A

0

B

H

E

N

n

R

E

S

E

T

RESETn

VDD

Summary of Contents for RD-JT51

Page 13: ...13 2 JT50 52 ...

Page 14: ...14 7 Packaging Description 1 JT51 ...

Page 15: ...15 2 JT50 52 ...

Page 16: ...16 8 Appearance Description ...

Page 53: ...ëí 5 PFC BOARD 6 DC DC BOARD ...

Page 54: ...ëì JT50 52 1 Final Assembly Trouble Shooting Guide ...

Page 55: ...ëë ...

Page 56: ...ëê 2 Engine Assembly Trouble Shooting Guide ...

Page 58: ...ëè 4 Power Supply Trouble Shooting Guide PFC BOARD DX850 DC DC BOARD ...

Page 59: ...5ç 5 DMD Block Trouble Shooting Guide ...

Page 60: ...êð ...

Page 74: ...éì Step 7 Download finished Step 8 Turn off the power switch ...

Page 81: ......