Chapter 3 BIOS Setup

35

User’s Manual

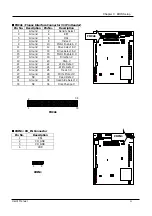

3.5 Chipset Features Setup

When you select the

CHIPSET FEATURES SETUP

on the main program, the screen display will appears as:

Chipset Features Setup Screen

Phoenix - Award BIOS CMOS Setup Utility

Advanced Chipset Features

Item Help

Menu Level

f

X

Spread Spectrum

DRAM Timing By SPD

Memory Hole

P2C/C2P Concurrency

System BIOS Cacheable

Video RAM Cacheable

Frame Butter Size

AGP Aperture Size

AGP-4X Mode

AGP Driving Control

AGP Driving Value

Panel Type

CPU to PCI Write Buffer

PCI Dynamic Bursting

PCI Master 0 WS Write

PCI Delay Transaction

PCI#2 Access #1 Retry

AGP Master 1 WS Write

AGP Master 1 WS Read

[Disabled]

[Enabled]

[Disabled]

[Enabled]

[Enabled]

[Enabled]

[8M]

[64M]

[Enabled]

[Auto]

[DA]

[1024

°

768 TFT 65Mhz]

[Enabled]

[Enabled]

[Enabled]

[Disabled]

[Enabled]

[Disabled]

[Disabled]

Ç

È

Æ

Move Enter: Select +/-/PU/PD: Value F10: Save Esc: Exit F1: General Help

F5: Previous Values F7: Optimized Defaults

Spread Spectrum: When the system clock generator pulses, the extreme values of the pulse generate excess

EMI. Enabling pulse spectrum spread modulation changes the extreme values from spikes to flat curves, thus

reducing EMI. This benefit may in some cases be outweighed by problems with timing-critical devices, such as a

clock-sensitive SCSI device.

DRAM Timing By SPD: This item allows you to select the value in this field, depending on whether the board

has paged DRAMs or EDO (extended data output) DRAMs.

Memory Hole: In order to improve performance, certain space in memory can be reserved for ISA cards.

This memory must be mapped into the memory space below 16MB.

P2C / C2P Concurrency: This item allows you to Enable or Disable the PCI to CPU, CPU to PCI concurrency.

The default setting is

Enabled

.

Summary of Contents for EM-568 Series

Page 4: ......

Page 8: ...Chapter 1 Introduction 4 User s Manual 1 5 Board Layout...