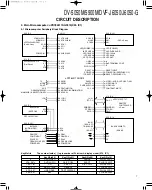

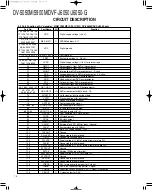

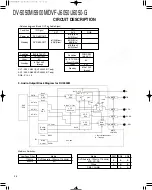

DV-5050M/5900M/DVF-J6050/J6050-G

12

CIRCUIT DESCRIPTION

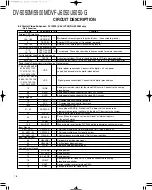

Port No.

Port Name

I/O

Function

47~51,54~59,61~65

HD0~HD15

I/O

DVD microcomputer data bus 0~15.

67

AUDSTR

I

Valid signal of bit stream input data.

68

ARQ

0

Unused.

69

VSTR

I

Clock signal input for bit stream.

71

VRQ

O

Request of program stream.

72

AVRTM

I

Sector separation signal.

74~78,80~82

STD0~STD7

I

Bit stream parallel input 0~7.

84

EXTCK

I

External FS384 input terminal.

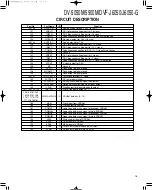

85

APLLVDD

-

Supply voltage (+2.5V) of internal logic for Audio PLL..

86

P5481

-

Audio PLL ground.

87

PHCOPMO

O

Audio PLL phase comparison output.

88

APLLAVSS

-

Audio PLL ground.

89

NC

-

Unused.

90

APLLAVDD

-

Supply voltage (+3.3V) for Audio PLL..

91

ACKIO

-

Connected to digital ground.

92

VSS

-

Digital ground.

93

DCTEST

-

Connected to digital ground.

94,95

TESTSEL1,0

-

Connected to digital ground.

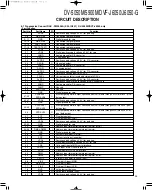

97~102,106,108,109

TEST4~TEST9

O

Unused.

TEST3,1,0

103

CLKMON

O

Unused.

107

RFF

O

Unused.

110

IECOUT

O

IEC958 format data output.

111

DMIX

O

Audio down mix signal output.

113

DACCK

O

Over sampling DAC clock output

114

LRCK

O

LR clock output.

115

SRCK

O

Bit clock output.

117~119

ADOUT(0~2)

O

Audio data output (0~2).

121

XPOWD

I

DAC power down control input.

122

VREFC

I

DAC reference voltage input for C signal.

123

IREFC

I

DAC bias current setting port for C signal.

124

COMPC

I

Capacitance connection for DAC (C signal) stabilization.

125

VCOUT

O

Unused.

126,136

AVDD

-

Analog supply voltage (+3.3V) for DAC.

127

VREFCB

I

DAC reference voltage input for CB signal.

I

DAC bias current setting port for CB signal.

I

Capacitance connection for DAC (CB signal) stabilization.

O

Unused.

-

Analog ground for DAC.

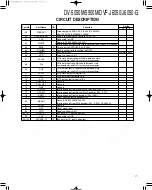

I

DAC reference voltage input for CR signal.

I

DAC bias current setting port for CR signal.

I

Capacitance connection for DAC (CR signal) stabilization.

O

Unused.

I

DAC reference voltage input for Y signal.

I

DAC bias current setting port for Y signal.

139

COMPY

I

Capacitance connection for DAC (Y signal) stabilization.

140

VYOUT

O

Unused.

143

XYSYNCO

I/O

Vertical synchronizing signal input/output.

144

XHSYNCO

I/O

Horizontal synchronizing signal input/output.

146

VCLK

O

Clock output for digital video data output.

148~155

VD0~VD7

O

Digital video data output (0~7).

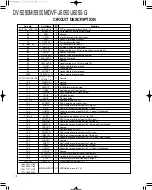

158,159,161,162

164,165,167,168

MDQ0~MDQ15

I/O

SDRAM data bus (0~15).

170,171,173,175

177,178,180,181

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299