RX-DP10VBK/RX-DP10VSL

RX-DP10RSL

1-36

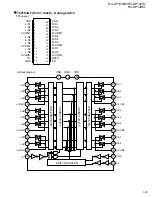

NC

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O1

I/O2

I/O3

Vss

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

V

DD

A15

CS2

WE

A13

A8

A9

A11

OE

A10

CS1

I/O8

I/O7

I/O6

I/O5

I/O4

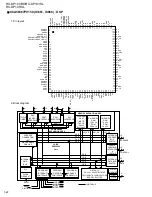

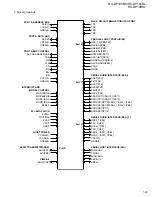

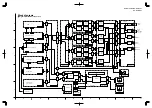

1. Pin layout

W24L010AJ-12 (IC668, IC669, IC670) : SRAM

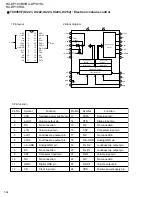

DECODER

CORE

ARRAY

CONTROL

DATA I/O

V

DD

Vss

CS2

CS1

OE

WE

A0

A16

I/O1

I/O8

2. Block diaglam

1. Block diaglam

3. Pin function

SYMBOL

A0 - A16

I/O1 - I/O8

CS1, CS2

WE

OE

V

DD

Vss

NC

DESCRIPTION

Address Input

Data Input/Output

Chip Select Inputs

Write Enable Input

Output Enable Input

Power Supply

Ground

No Connection

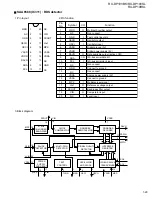

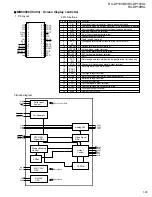

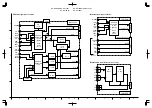

1CLR 1

1D

2

1CK

3

1PR

4

1Q

5

1Q

6

GND

V

CC

2CLR

2D

2CK

2PR

2Q

2Q

7

14

13

12

11

10

9

8

(TOP VIEW)

CK

Q

D

Q

CK

Q

D

Q

TC74VHC74FT (IC683) : Flip-flop

1. Pin layout

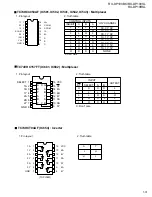

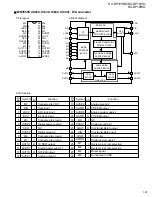

1. Pin layout

1

2

3

4

8

7

6

5

VCC

PR

CLR

Q

CK

D

Q

GND

TC7WH74FU (IC659, IC684) : Clock buffer

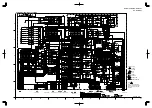

3

2

5

1

DC INPUT(Vin)

GND

DC OUTPUT(Vo)

CUSTOM IC

ON/OFF CONTROL(Vc)

PQ3DZ53 (IC691, IC692, IC693, IC695, IC696) : Regulator IC

Summary of Contents for RX-DP10RSL

Page 61: ...RX DP10VBK RX DP10VSL RX DP10RSL 3 2 M E M O ...

Page 94: ...RX DP10VBK BX DP10VSL RX DP10RSL 3 35 M E M O ...

Page 97: ...RX DP10VBK RX DP10VSL RX DP10RSL 3 38 M E M O ...

Page 99: ...RX DP10VBK RX DP10VSL RX DP10RSL 3 40 M E M O ...

Page 130: ...RX DP10VBK BX DP10VSL RX DP10RSL 3 71 M E M O ...