RX-DP10VBK/RX-DP10VSL

RX-DP10RSL

1-16

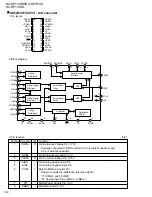

Note 1: All input pins except internal pull-down pins should not be left floating.

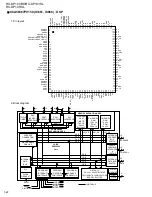

1.Pin layout

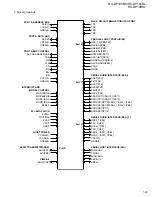

2.Pin function

AK4112 (IC673) : Digital audio receiver

DVDD

DVSS

TVDD

V/TX

XTI

XTO

PDN

R

AVDD

AVSS

RX1

RX2/DIF0

RX3/DIF1

RX4/DIF2

CM0/CDTO

CM1/CDT1

OCKS1/CCLK

OCKS0/CSN

MCKO1

MCKO2

DAUX

BICK

SDTO

LRCK

ERF

FS96

P/SN

AUTO

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

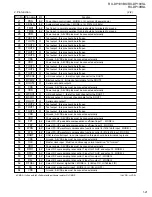

Symbol

DVDD

DVSS

TVDD

V

TX

XTI

XTO

PDN

R

AVDD

AVSS

RX1

DIF0

RX2

DIF1

RX3

DIF2

RX4

AUTO

P/S

FS96

ERF

LRCK

SDTO

BICK

DAUX

MCK02

MCK01

OCKS0

CSN

OCKS1

CCLK

CM1

CDTI

CM0

CDTO

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

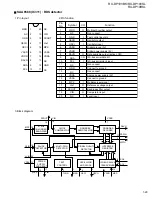

Function

Digital Power Supply Pin, 3.3V

Digital Ground Pin

Input Buffer Power Supply Pin, 3.3V or 5V

Validity Flag Output Pin in Parallel Mode

Transmit channel (through data) Output Pin in Serial Mode

X'tal Input Pin

X'tal Output Pin

Power-Down Mode PIn

When "L", the AK4112A is powered-down and reset.

External Resistor Pin

18k +/-1% resistor to AVSS externally.

Analog Power Supply Pin

Analog Ground Pin

Receiver Channel 1

This channel is selected in Parallel Mode or default of Serial Mode.

Audio Data Interface Format 0Pin in Parallel Mode

Receiver Channel 2 in Serial Mode

Audio Data Interface Format 1 Pin in Parallel Mode

Receiver Channel 3 in Serial Mode

Audio Data Interface Format 2 Pin in Parallel Mode

Receiver Channel 4 in Serial Mode

Non-PCM Detect Pin

"L": No detect, "H": Detect

Parallel/Serial Select Pin

"L": Serial Mode, "H": Parallel Mode

96kHz Sampling Detect Pin

(RX Mode) "H": fs=88.2kHz or more, "L": fs=54kHz or less.

(X'tal Mode) "H": XFS96=1, "L": XFS96=0.

Unlock & Parity Error Output Pin

"L": No Error, "H": Error

Output Channel Clock Pin

Audio Serial Data Output Pin

Audio Serial Data Clock Pin

Auxiliary Audio Data Input Pin

Master Clock #2 Output Pin

Master Clock #1 Output Pin

Output Clock Select 0 Pin in Parallel Mode

Chip Select Pin in Serial Mode

Output Clock Select 1 Pin in Parallel Mode

Control Data Clock Pin in Serial Mode

Master Clock Operation Mode Pin0 in Parallel Mode

Control Data Input Pin in Serial Mode

Master Clock Operation Mode Pin1 in Parallel Mode

Control Data Output Pin in Serial Mode

I/O

-

-

-

O

O

I

O

I

-

-

-

I

I

I

I

I

I

I

O

I

O

O

I/O

O

I/O

I

O

O

I

I

I

I

I

I

I

O

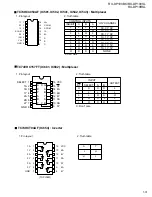

Description of major ICs

Summary of Contents for RX-DP10RSL

Page 61: ...RX DP10VBK RX DP10VSL RX DP10RSL 3 2 M E M O ...

Page 94: ...RX DP10VBK BX DP10VSL RX DP10RSL 3 35 M E M O ...

Page 97: ...RX DP10VBK RX DP10VSL RX DP10RSL 3 38 M E M O ...

Page 99: ...RX DP10VBK RX DP10VSL RX DP10RSL 3 40 M E M O ...

Page 130: ...RX DP10VBK BX DP10VSL RX DP10RSL 3 71 M E M O ...