REL0.1

Page 11 of 52

Snapdragon 820 SMARC SOM Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

2.

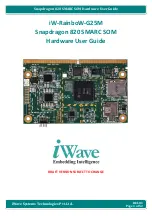

ARCHITECTURE AND DESIGN

This section provides detailed information about the Snapdragon 820 SMARC SOM features and Hardware architecture

with high level block diagram.

2.1

Snapdragon 820 SMARC SOM Block Diagram

Micro SD

Connector

CPU

APQ8096

LPDDR4 PoP-3GB

(Upgradable)

iW-RainboW-G25M - APQ8096 SMARC SOM Block Diagram

eMMC

–

32GB

(Upgradable)

MMC(8bit)

EBI0

EBI1

SDC1

SD (4bit)

LPDDR4 (64bit)

SDC4

BLSP2, 8, 9,

10,11,12

HDMI

USB_SS

PCIe0

PCIe2

PCIe1

SLIMbus

PCM1/

MI2S_1

JTAG

PMIC

Interfaces

SMARC Edge

Connector

100Pin

Expansion

Connector

Audio Codec

(Optional)

WiFi + BT

PMIC &

Battery

Charger

CCI_I2C2

BLSP2-UART

PCIe to Gigabit

Ethernet

PCIe x 1

USB3.0

USB2_HS

USB2.0 x 1

USB1_HS

USB Device x 1

PCIe

USB HUB

(4Ports)

USB2.0

USB2.0 x 4

Gigabit

Ethernet

MI2S_2,

MI2S_3

MI2S x 2

HDMI x 1

GNSS

GNSS (GPS)

RF Receiver &

Antenna Conn

GNSS

SDC2

SD x 1

BLSP7_I2C,

BLSP8-I2C

I2C x 2

MPI CSI0,

MIPI_CSI1

MPI_CSI X 2

BLSP1_SPI

SSC_SPI_1

SPI x 2

MIPI Camera x 1 (4lane each)

I2C x 1 (for Camera)

GPIOs

GPIOs, Control & Status Signals

JTAG Header

(Optional)

2Pin Power IN

(Optional)

Battery Header

(Optional)

UART x 6

JTAG

Power to

Peripherals

5V

3.7V

GPIOs

GPIOs

SLIMbus

Audio

In/Out

PCIe

UART

PCM

Wi-Fi Antenna

PCIe2

2

¹ If On-SOM WIFI+BT is used, PCIe0 cannot be used on Qseven Edge.

UFS

UFS Flash

(Optional)

UFS

GNSS Antenna

Connector

MPI DSI0,

MIPI_DSI1

MIPI_DSI x 2

CCI_I2C0,

CCI_I2C1

I2C x 2 (for Camera)

MPI CSI2

USB3.0 x 2

PCIe0

¹

SSC

SSC_I2Cx1, SSC_UARTx3

Figure 1: Snapdragon 820 SMARC SOM Block Diagram