Chapter 4 System Support

4.2.2 PCI BUS MASTER ARBITRATION

The PCI bus supports a bus master/target arbitration scheme. A bus master is a device that has

been granted control of the bus for the purpose of initiating a transaction. A target is a device that

is the recipient of a transaction. The Request (REQ), Grant (GNT), and FRAME signals are used

by PCI bus masters for gaining access to the PCI bus. When a PCI device needs access to the PCI

bus (and does not already own it), the PCI device asserts its REQ

n

signal to the PCI bus arbiter (a

function of the system controller component). If the bus is available, the arbiter asserts the GNT

n

signal to the requesting device, which then asserts FRAME and conducts the address phase of the

transaction with a target. If the PCI device already owns the bus, a request is not needed and the

device can simply assert FRAME and conduct the transaction. Table 4-2 shows the grant and

request signals assignments for the devices on the PCI bus.

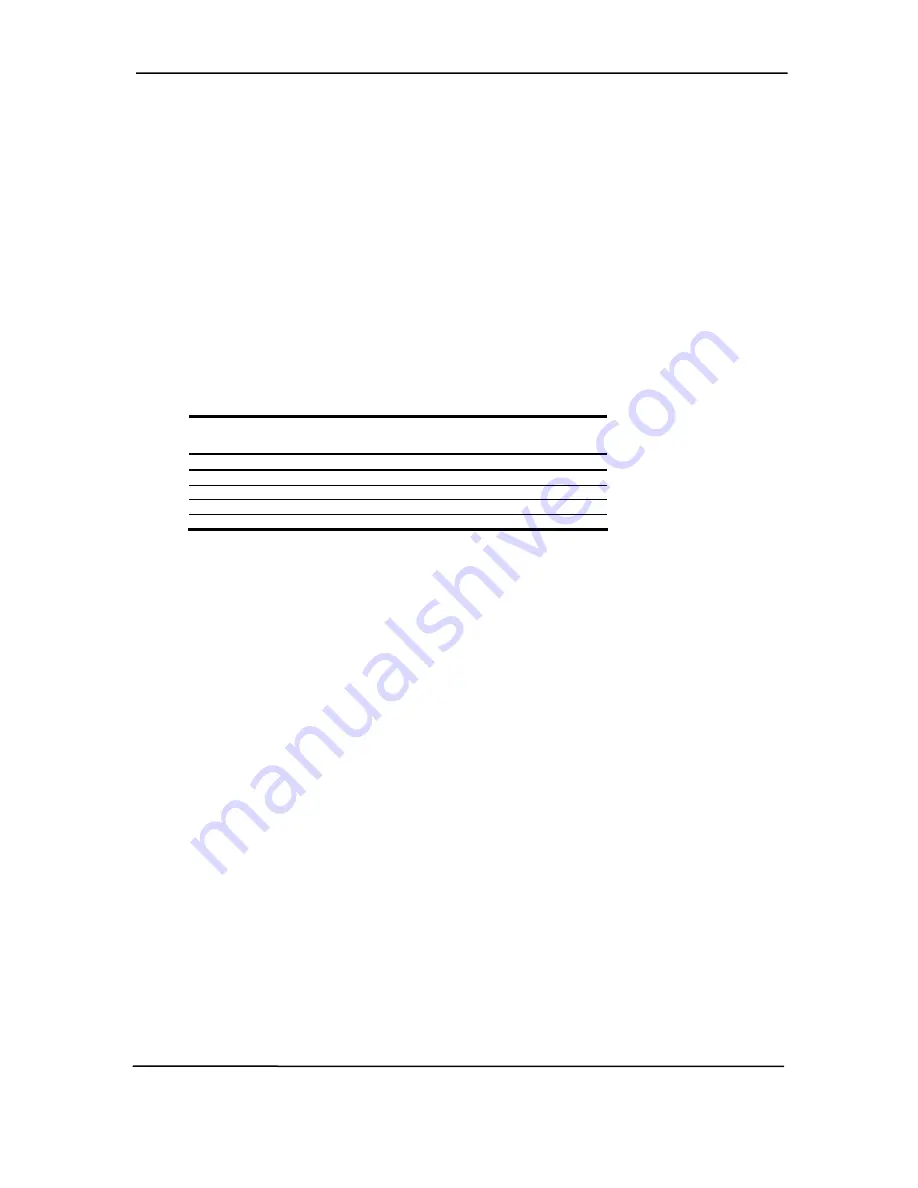

Table 4-2. PCI Bus Mastering Devices

Table 4-2.

PCI Bus Mastering Devices

REQ/GNT Line

Device

REQ0/GNT0

PCI Connector Slot 1

REQ1/GNT1

PCI Connector Slot 2

REQ2/GNT2

PCI Connector Slot 3

GREQ/GGNT

AGP Slot

NOTE:

PCI bus arbitration is based on a round-robin scheme that complies with the fairness algorithm

specified by the PCI specification. The bus parking policy allows for the current PCI bus owner

(excepting the PCI/ISA bridge) to maintain ownership of the bus as long as no request is asserted

by another agent. Note that most CPU-to-DRAM and AGP-to-DRAM accesses can occur

concurrently with PCI traffic, therefore reducing the need for the Host/PCI bridge to compete for

PCI bus ownership.

Compaq D315 and hp d325 Personal Computers

Featuring the AMD Athlon XP Processor

Second Edition – April 2003

4-6