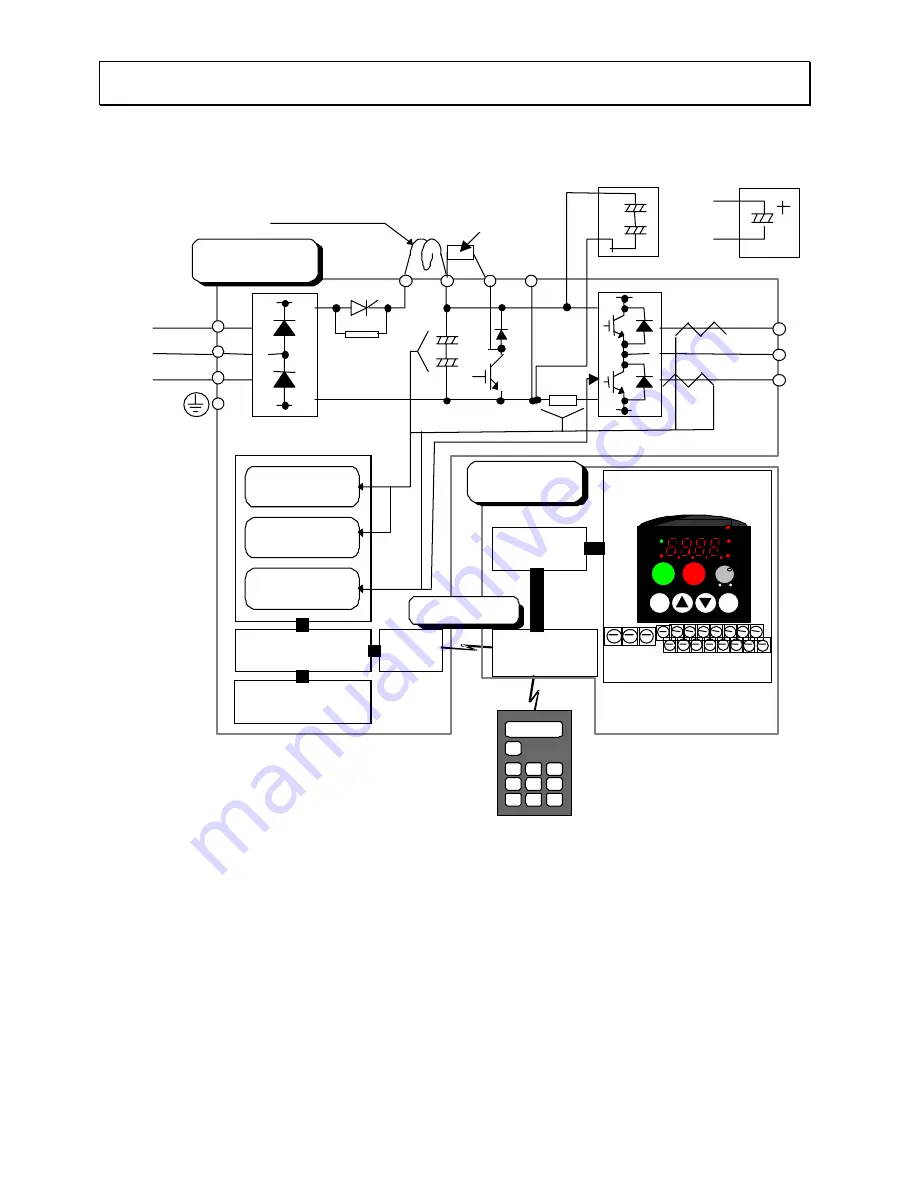

9. Image block diagram

(1). IMAGE BLOCK DIAGRAM OF SJ100 INVERTER

MCU

REMORT OPERATOR

ISORATION

DC REACTOR

(OPTION)

N(-)

PD(+1)

P(+)

T(L3)

S(L2)

R(L1)

INVERTER

CONVERTER

*1

W(T3)

V(T2)

U(T1)

DRIV E CIRCUIT

DETECT V,I

POWER SUPPLY

MCU

EEPROM

COMMUNICATION

PORT

CORE INV ERTER

(ISPM)

SERIAL

COMMUNICATION

HITACHI

USER INTERFACE

I/O BLOCK

(I/O board)

TERMINALS

OPERATION PANEL WITH

POTEN TIO METER

SUB CONDENCER BOARD(HFx)

+

C B

+

+

RS

(LFU,NFE)

Tr BR

RB

BRD resistor(option)

EMC DIRECTIVE COMPLIANT WITH DEDICATED NOISE FILTER(OPTION)

Note; Main circuit capacitor CB; HFE,HFU; serial connection.

; LFU,NFE; single connection.

9-1/E

Summary of Contents for SJ100 Series

Page 3: ...Revisions Revision history table No Revision contents Date of issue Manual No ⅰⅰ ...

Page 40: ......

Page 56: ......

Page 57: ......

Page 58: ......

Page 59: ......

Page 60: ......

Page 61: ......

Page 62: ......

Page 63: ......

Page 64: ......

Page 65: ......

Page 66: ......

Page 67: ......

Page 68: ......

Page 69: ......

Page 70: ......

Page 71: ......

Page 72: ......

Page 73: ......

Page 74: ......

Page 75: ...End of page ...