42

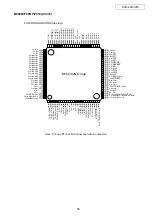

DVD-2910/955

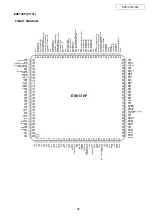

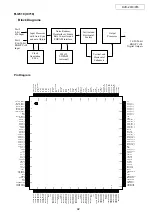

FLI2310 (IC718)

B

lock

D

iagrams

Input Processor

with Auto Sync

and auto Adjust

Noise Reducer,

Deinterlacer, Frame

Rate Converter and

SDRAM interface

Port 2

8-bit

656 Input

Port 1

8/16/24-bit

RGB/YCrCb

Input

Clock

Generation

PLLs

2Mx32

SDRAM

(external)

Vertical and

Horizontal

Scalers

Vertical and

Horizontal

Enhancers

Output

Processor

16/20/24-bit

RBG/YCrCb

Digital Outputs

Pin Diagram

1 5 5

1 5 0

1 4 5

1 4 0

1 3 5

1 3 0

1 2 5

1 2 0

1 1 5

1 1 0

1 0 5

1

5

1 0

1 5

2 0

2 5

3 0

3 5

4 0

4 5

5 0

5 5

6 5

6 0

1 0 0

9 5

9 0

8 5

8 0

7 5

7 0

2 0 5

1 9 5

2 0 0

1 6 0

1 6 5

1 7 0

1 7 5

1 8 0

1 8 5

1 9 0

HSYNC1_PORT1

VDD1

B/Cb/D1_0

VSS

IN_CLK1_PORT1

FIELD ID1_PORT1

VSYNC1_PORT1

HSYNC2_PORT1

IN_CLK2_PORT1

FIELD ID2_PORT1

VSYNC2_PORT1

B/Cb/D1_6

B/Cb/D1_5

B/Cb/D1_4

B/Cb/D1_3

B/Cb/D1_2

B/Cb/D1_1

B/Cb/D1_7

VDDcore1

VSScore

R/Cr/Cb Cr_0

R/Cr/Cb Cr_6

R/Cr/Cb Cr_5

R/Cr/Cb Cr_4

R/Cr/Cb Cr_3

R/Cr/Cb Cr_2

R/Cr/Cb Cr_1

R/Cr/Cb Cr_7

VDD2

VSS

G/Y/Y_0

G/Y/Y_1

G/Y/Y_6

G/Y/Y_5

G/Y/Y_4

G/Y/Y_3

G/Y/Y_2

G/Y/Y_7

VDDcore2

VSScore

IN_SEL

TEST

DEV_ADDR1

DEV_ADDR0

SCLK

SDATA

RESET_N

VDD3

VSS

SDRAM DATA(0)

SDRAM DATA(2)

SDRAM DATA(1)

S

DRAM

DA

T

A

(3

)

S

DRAM

DA

T

A

(1

0

)

S

DRAM

DA

T

A

(9

)

SDRA

M

DATA(8)

SDRA

M

DATA(7)

SDRA

M

DATA(6)

S

DRAM

DA

T

A

(5

)

S

DRAM

DA

T

A

(4

)

S

DRAM

DA

T

A

(1

7

)

S

DRAM

DA

T

A

(1

6

)

S

DRAM

DA

T

A

(1

5

)

S

DRAM

DA

T

A

(1

4

)

S

DRAM

DA

T

A

(1

2

)

S

DRAM

DA

T

A

(1

3

)

S

DRAM

DA

T

A

(1

1

)

VDD4

VS

S

V

DDcore3

VS

Sc

o

re

S

DRAM

DA

T

A

(2

0

)

S

DRAM

DA

T

A

(1

9

)

S

DRAM

DA

T

A

(1

8

)

SDRA

M

DATA(31)

S

DRAM

DA

T

A

(3

0

)

S

DRAM

DA

T

A

(2

9

)

S

DRAM

DA

T

A

(2

8

)

S

DRAM

DA

T

A

(2

6

)

S

DRAM

DA

T

A

(2

7

)

S

DRAM

DA

T

A

(2

5

)

SDRA

M

DATA(24)

S

DRAM

DA

T

A

(2

3

)

S

DRAM

DA

T

A

(2

1

)

S

DRAM

DA

T

A

(2

2

)

V

DDcore4

VS

Sc

o

re

VS

S

VDD5

TES

T

IN

SDRA

M

ADDR(10)

SDRA

M

ADDR(5)

SDRA

M

ADDR(4)

SDRA

M

ADDR(3)

S

DRAM

A

DDR(

6

)

SDRA

M

ADDR(7)

SDRA

M

ADDR(8)

SDRA

M

ADDR(9)

V

DDcore5

VS

Sc

o

re

SDRA

M

ADDR(0)

SDRA

M

ADDR(1)

SDRA

M

ADDR(2)

SDRA

M

WE

N

B/U/Pb_OUT_7

VDDcore7

VSScore

R/V/Pr_OUT_7

VDD8

VSS

G/Y/Y_OUT_7

G/Y/Y_OUT_1

G/Y/Y_OUT_2

G/Y/Y_OUT_3

G/Y/Y_OUT_4

G/Y/Y_OUT_5

G/Y/Y_OUT_6

G/Y/Y_OUT_0

R/V/Pr_OUT_0

R/V/Pr_OUT_1

R/V/Pr_OUT_2

R/V/Pr_OUT_3

R/V/Pr_OUT_4

R/V/Pr_OUT_5

R/V/Pr_OUT_6

B/U/Pb_OUT_0

B/U/Pb_OUT_1

B/U/Pb_OUT_2

B/U/Pb_OUT_3

B/U/Pb_OUT_4

B/U/Pb_OUT_5

B/U/Pb_OUT_6

VSS

VDD7

CLKOUT

VSScore

VDDcore6

TEST OUT1

CTLOUT4

CTLOUT0

CTLOUT1

CTLOUT2

CTLOUT3

TEST OUT0

TEST3

SDRAM CLKIN

SDRAM CLKOUT

VSS

VDD6

SDRAM DQM

SDRAM CASN

SDRAM BA1

SDRAM BA0

SDRAM CSN

SDRAM RASN

OE

P

LL_PV

DD

P

LL_PV

SS

A

V

S

S

_P

LL_BE

1

AV

DD_PLL_B

E1

AV

SS

_PLL_S

DI

A

V

S

S

_P

LL_F

E

AV

SS

_PLL_B

E2

A

V

D

D

_

P

LL_F

E

A

V

DD_P

LL_SDI

A

V

DD_P

LL_BE

2

R_VS

S

R_VDD1.8

R_

V

S

S

Res

e

rv

ed

Re

se

rv

e

d

Res

e

rv

ed

R_

V

D

D

R_

VDD

R_

V

D

D

R_VS

S

R_VS

S

R_VS

S

Res

e

rv

ed

Res

e

rv

ed

Re

se

rv

e

d

R_VS

S

R_

VDD

R_

V

S

S

R_VS

S

R_

V

D

D

R_

VDD

TES

T

0

TES

T

1

TES

T

2

XT

AL

I

N

XT

AL

O

U

T

V

DD9

VS

S

HSY

NC_

PORT

2

IN

_C

LK_P

OR

T2

FIELD ID_P

O

R

T2

V

S

Y

NC_

PORT

2

VS

Sc

or

e

V

DDcore8

D

1_IN

_0

D

1_IN

_7

D

1_IN

_6

D

1_IN

_5

D

1_IN

_4

D

1_IN

_3

D

1_IN

_2

D

1_IN

_1

Summary of Contents for DVD-2910

Page 29: ...29 DVD 2910 955 BLOCK DIAGRAM ...

Page 48: ...48 DVD 2910 955 CXD2753R IC602 Pin Assignment Block Diagram ...

Page 79: ...79 DVD 2910 955 TA76432FC IC902 PC123 IC909 COLLECTOR EMITTER ANODE CATHODE TOP VIEW ...

Page 81: ...81 DVD 2910 955 PRINTED WIRING BORDS GU 3612 MAIN PWB P W B UNIT ASS Y COMPONENT SIDE ...

Page 82: ...82 DVD 2910 955 GU 3612 MAIN PWB P W B UNIT ASS Y FOIL SIDE ...

Page 83: ...83 DVD 2910 955 GU 3615 VODEO P W B UNIT ASS Y COMPONENT SIDE ...

Page 84: ...84 DVD 2910 955 GU 3615 VODEO P W B UNIT ASS Y FOIL SIDE ...

Page 85: ...85 DVD 2910 955 GU 3616 AUDIO POWER P W B UNIT ASS Y COMPONENT SIDE ...

Page 86: ...86 DVD 2910 955 GU 3616 AUDIO POWER P W B UNIT ASS Y FOIL SIDE ...

Page 117: ...DVD 2910 955 117 GU 3615 1 VIDEO P W B V6 V7 V8 V1 V2 V3 V4 V5 ...