AW86225

October 2021 V1.9

www.awinic.com

8 Copyright © 2020 SHANGHAI AWINIC TECHNOLOGY CO., LTD

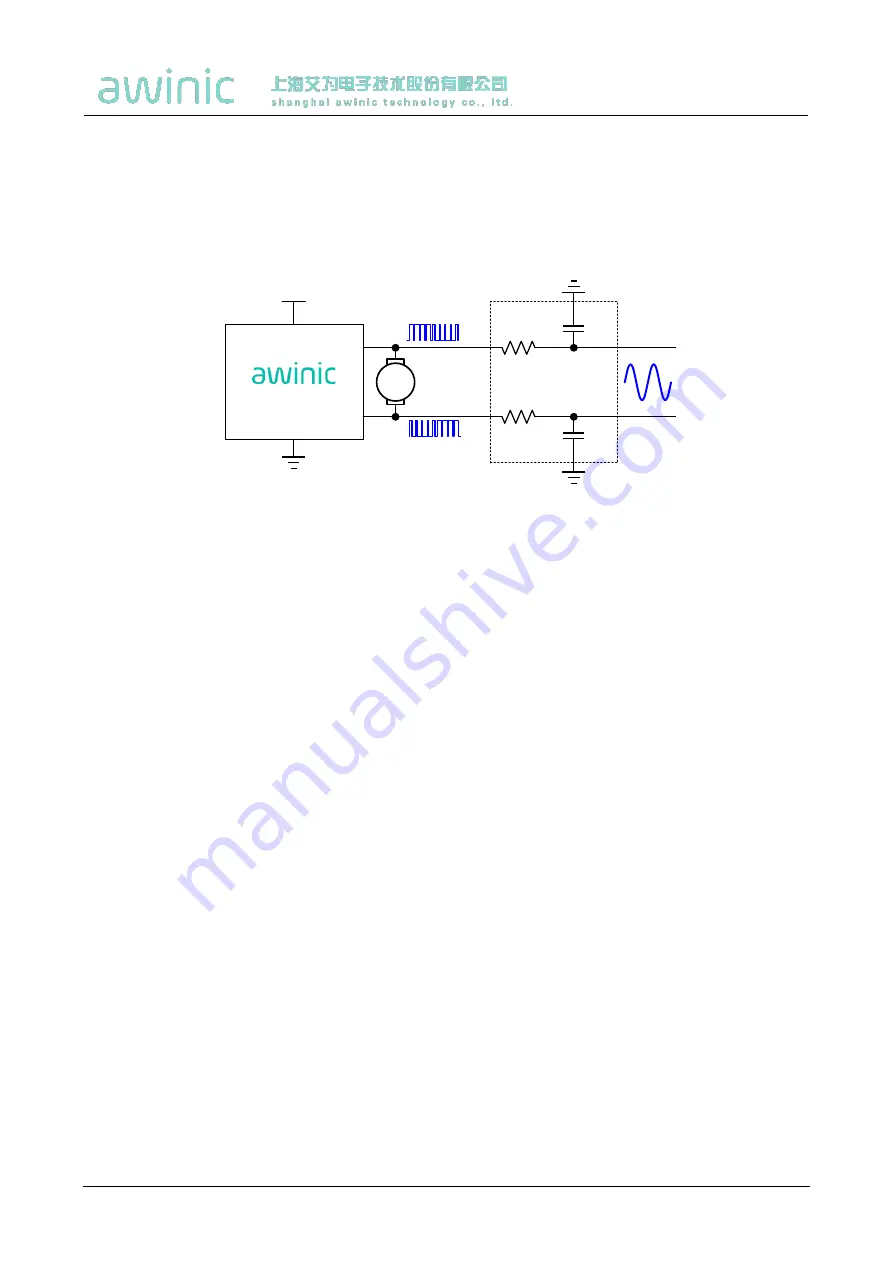

Measurement Setup

AW86225 features switching digital output, as shown in Figure 6. Need to connect a low pass filter to HDP/HDN

output respectively to filter out switch modulation frequency, then measure the differential output of filter to

obtain analog output signal.

HDP

HDN

AW86225

3.4kHz

Low-Pass Fliter

100k

Ω

100k

Ω

0.47nF

0.47nF

LRA

Figure 6 AW86225 test setup

awinic Confidential