Page 10

6.1.2

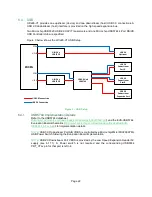

PL I/Os (Banks 26, 65, 66)

Zynq Ult MPSoC Promammable Logic (PL) provides two types of I/O banks: High-

density (HD) banks and high-performance (HP) banks. HD banks support a limited number of

single-ended I/O standards with speeds up to 250Mbps and VCCO voltages up to 3.30V. HP

banks support a large variety of high-speed I/O standards, including differential I/O, and support

VCCO voltages up to 1.80V.

ZU3EG provides one HD bank (Bank 26) with 24 pins, one HP bank (Bank 65) with 52 pins,

and another HP bank (Bank 66) with 6 pins.

The PL I/Os on Ultra96-V1 are tied to the Low-Speed 96Boards Mezzanine, the High-Speed

96Boards Mezzanine, Bluetooth, and the fan.

Table 1 – PL IO Bank 26

MPSoC Pin Number Bank

MPSoC Site Name

Function

C8

26

IO_L8P_HDGC_AD4P_26

Bluetooth

A8

IO_L10P_AD2P_26

A9

IO_L9N_AD3N_26

B9

IO_L9P_AD3P_26

B5

IO_L11N_AD1N_26

B7

IO_L12P_AD0P_26

E8

IO_L6P_HDGC_AD6P_26

HS Expansion

D8

IO_L6N_HDGC_AD6N_26

D7

IO_L5P_HDGC_AD7P_26

LS Expansion

F8

IO_L4P_AD8P_26

E5

IO_L3N_AD9N_26

D6

IO_L5N_HDGC_AD7N_26

D5

IO_L7P_HDGC_AD5P_26

C7

IO_L8N_HDGC_AD4N_26

B6

IO_L11P_AD1P_26

C5

IO_L7N_HDGC_AD5N_26

F7

IO_L4N_AD8N_26

G7

IO_L2P_AD10P_26

F6

IO_L2N_AD10N_26

G5

IO_L1N_AD11N_26

A6

IO_L12N_AD0N_26

A7

IO_L10N_AD2N_26

G6

IO_L1P_AD11P_26

E6

IO_L3P_AD9P_26