Page 30

8.4

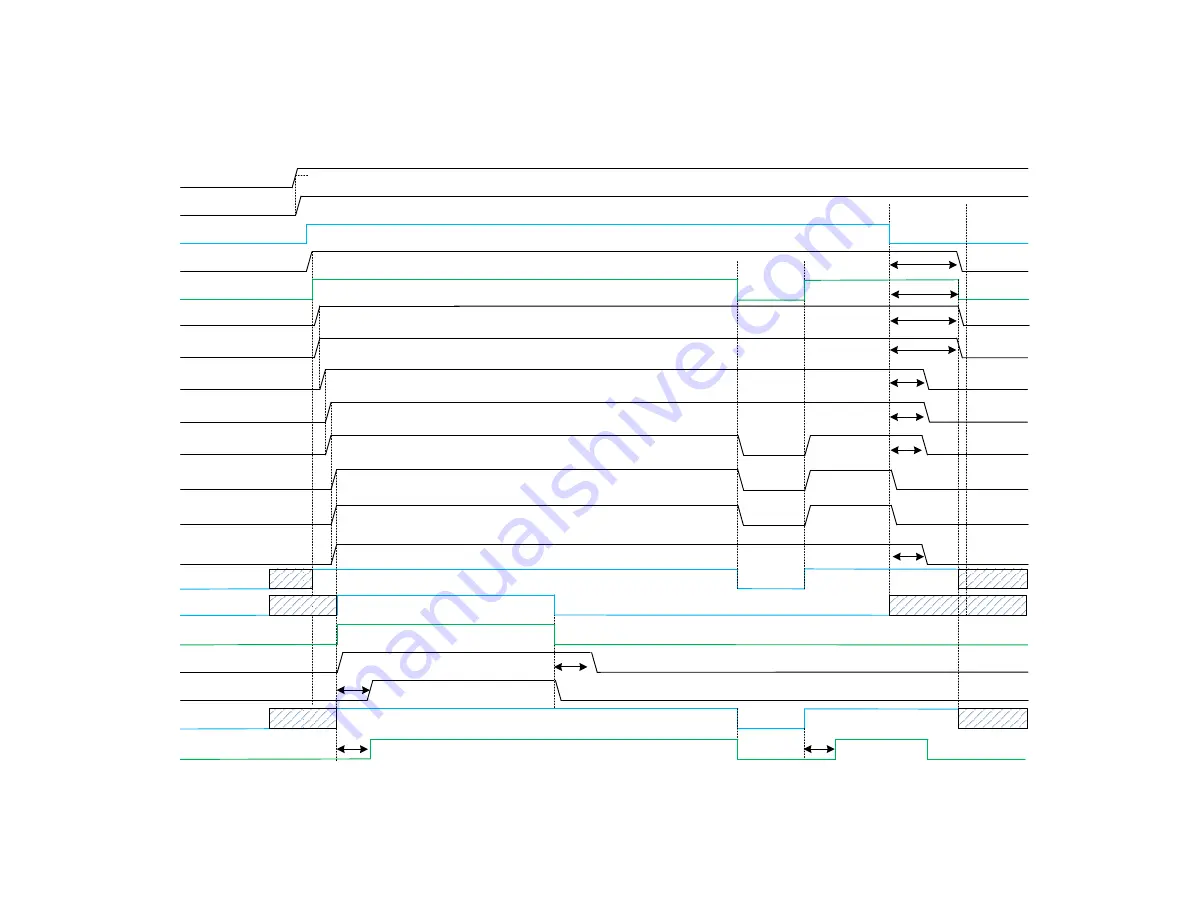

Power Sequence

The diagram below shows the power sequence:

Figure 9 – Ultra96-V1 Power Sequencing

CTL4* (POWER_EN)

BUCK2 (VC others)

BUCK1 (VCC_5V0)

4 ms

BUCK5 (VCC_1V2)

VTT LDO (MGTRAVCC)

BUCK6 (VCC_PSAUX)

LDOA2 (VCC_PSPLL)

BUCK4 (VCC_3V3)

BUCK3 (VCCO_PSDDR)

0.85 V

5 V

1.2 V

0.9 V

1.2 V

3.3 V

1.1 V

1.8 V

2 ms

4 ms

GPO1* (VCC_PSINTFP enable)

2 ms

4 ms

CTL5 (PL_PWR_EN)

GPO4 (VCCINT enable)

4 ms

SWB1_2 (VCCAUX)

1.8 V

LDOA3 (VCCO_HP)

1.2 V

CTL3 (

PS_LP_PWR_EN

)

VSYS

5.6V

LDO5V / LDO3P3 /

I

2

C Available

LDOA1 (MGTRAVTT)

1.8 V

GPO3* (PS_POR_B)

2 ms

2 ms

2 ms

2.5 ms

CTL1 (

PS_POR_PB_B

)

2.5 ms

2 ms