Trace

7-4

ICE50 User Guide

2523A–AVR–11/02

7.3

Contents of

Trace Window

Based on

Instruction

(ICE50)

As can be seen from Enabling Trace, the contents of the different columns varies with

which instruction is being executed. This section describes how to interpret the contents

of the Trace buffer based on which instruction is being executed.

Some of the explanations are tagged with a number. This number indicates the cycle

number in the instruction execution (important for multi-cycle instructions only). The

term N/A is used when a field does not contain any valuable information.

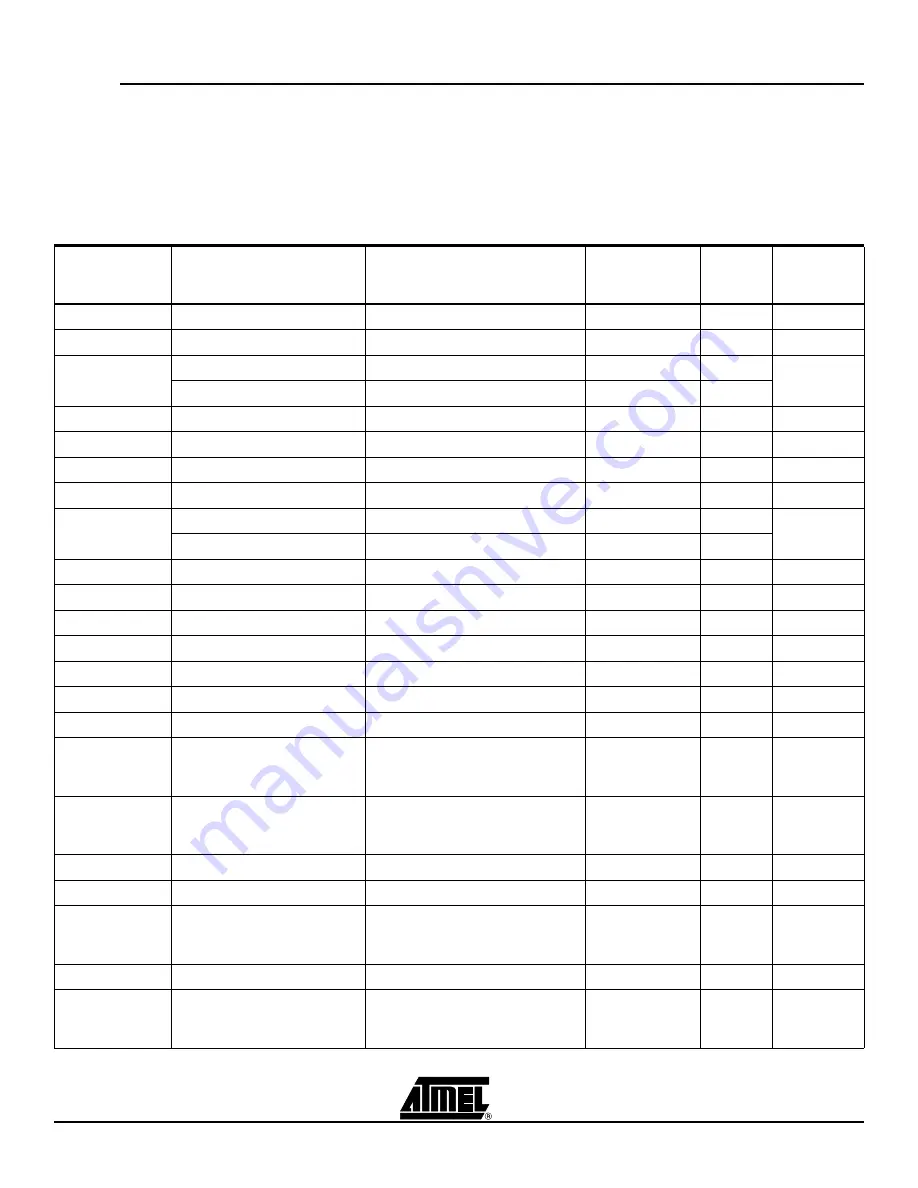

Table 7-1. Arithmetic and Logic Instructions

Instruction

INSTA[0..15]

PMem Addr

[PC[A0..22]

Reg.Val

RegFileL[0..7]

Dat.Addr

RAM_EEADDR

[0..22]

Dat.Val

Status

Register

ADD Rd,Rr

Address of instruction

Result of addition

N/A

N/A

Z,C,N,V,S,H

ADC Rd, Rr

Address of instruction

Result of addition

N/A

N/A

Z,C,N,V,S,H

ADIW Rdl,K

1. Address of instruction

1. Result of addition, low byte

1. N/A

1. N/A

Z,C,N,V,S

2. Address of next instruction

2. Result of addition, high byte

2. N/A

2. N/A

SUB Rd, Rr

Address of instruction

Result of subtraction

N/A

N/A

Z,C,N,V,S,H

SUBI Rd, K

Address of instruction

Result of subtraction

N/A

N/A

Z,C,N,V,S,H

SBC Rd, Rr

Address of instruction

Result of subtraction

N/A

N/A

Z,C,N,V,S,H

SBCI Rd, K

Address of instruction

Result of subtraction

N/A

N/A

Z,C,N,V,S,H

SBIW Rdl,K

1. Address of instruction

1. Result of subtraction, low byte

1. N/A

1. N/A

Z,C,N,V,S,H

2. Address of next instruction

2. Result of subtraction, high byte

2. N/A

2. N/A

AND Rd, Rr

Address of instruction

Result of logical AND

N/A

N/A

Z,N,V,S

ANDI Rd, K

Address of instruction

Result of logical AND

N/A

N/A

Z,N,V,S

OR Rd,Rr

Address of instruction

Result of logical OR

N/A

N/A

Z,N,V,S

ORI Rd, K

Address of instruction

Result of logical OR

N/A

N/A

Z,N,V,S

EOR Rd, Rr

Address of instruction

Result of logical EOR

N/A

N/A

Z,N,V,S

COM Rd

Address of instruction

Result of complement

N/A

N/A

Z,C,N,V,S

NEG Rd

Address of instruction

Result of negation

N/A

N/A

Z,C,N,V,S,H

SBR Rd,K

Will never appear (is

disassembled to ORI

instruction)

N/A

N/A

N/A

Z,N,V,S

CBR Rd,K

Will never appear (is

disassembled to ANDI

instruction)

N/A

N/A

N/A

Z,N,V,S

INC Rd

Address of instruction

Result of incrementation

N/A

N/A

Z,N,V,S

DEC Rd

Address of instruction

Result of decrementation

N/A

N/A

Z,N,V,S

TST Rd

Will never appear (is

disassembled to AND

instruction)

N/A

N/A

N/A

Z,N,V,S

CLR Rd

Address of instruction

Result (always 0x00)

N/A

N/A

Z,N,V,S

SER Rd

Will never appear (is

disassembled to LDI

instruction)

N/A

N/A

N/A

N/A

Summary of Contents for ICE50

Page 1: ...ICE50 User Guide ...

Page 2: ......

Page 10: ...Preface 1 4 ICE50 User Guide 2523A AVR 11 02 ...

Page 14: ...Introduction 2 4 ICE50 User Guide 2523A AVR 11 02 ...

Page 48: ...Configuring AVR Studio 5 10 ICE50 User Guide 2523A AVR 11 02 Figure 5 11 ICE Staus Window ...

Page 52: ...Configuring AVR Studio 5 14 ICE50 User Guide 2523A AVR 11 02 Figure 5 15 Version Information ...

Page 70: ...Trace 7 16 ICE50 User Guide 2523A AVR 11 02 ...

Page 72: ...Troubleshooting 8 2 ICE50 User Guide 2523A AVR 11 02 ...