CYC1000 User Guide

www.arrow.com

Page | 12

January 2020

3.3.2

Push Buttons

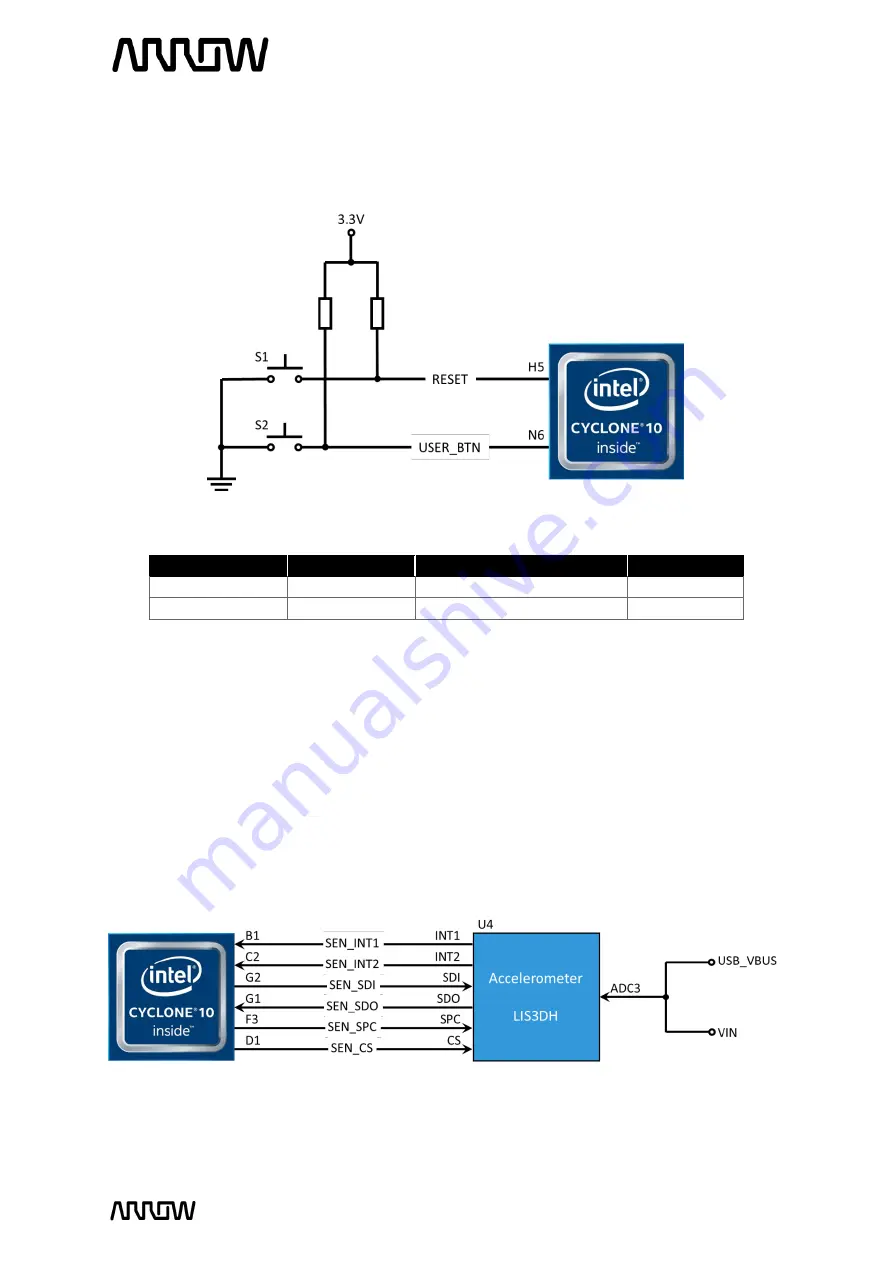

The board has two push buttons connected to the FPGA. Push buttons drive their associated pins

low logic level when pressed and high logic level when released.

Board Reference

FPGA Pin No.

Description

I/O Standard

RESET

PIN_H5

nCONFIG

3.3 V

USER_BTN

PIN_N6

User button

3.3 V

3.3.3

Accelerometer

The board comes with a digital accelerometer (LIS3DH), commonly known as the G-Sensor. This

G-Sensor is a small, thin, ultra-low power consumption, 3-axis accelerometer with digital I2C/SPI

serial interface, standard output. The LIS3DH has user-selectable full scales of +/-2g, +/-4g, +/-8g,

+/-16g and it is capable of measuring accelerations with output data rates from 1 Hz to 5 kHz. The

supplied power to the board (coming either from micro-USB connection or user V

in

) can be

monitored through the ADC channel 3 of the accelerometer.

Figure 6

–

Button Connections

Figure 7

–

Accelerometer Connections