Source

Schematic Signal

Name

Frequency

I/O

Standard

Device / Pin

Number

Application

U14

CLK125M

125.000 MHz

3.3 V

CMOS

MAX 10/K22 Programmable

default 125 MHz

clock for PLL

generating required

clocks for LVDS

GPIO interface

U14

CLK100M_LPDDR2 100.000 MHz

3.3 V

CMOS

MAX 10/E10

LPDDR2 clock

U15

CLK50M_MAX10

50.000 MHz

3.3 V

CMOS

MAX 10/J10

MAX 10 clock

U15

CLK50M_MAXII

50.000 MHz

3.3 V

CMOS

MAX II/L1

MAX II clock

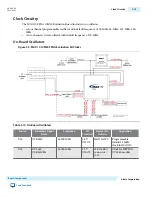

Off-Board Clock Input/Output

The MAX 10 10M50 Evaluation Board has input and output clocks which can be driven onto the board.

Resistor reworking might be needed for specific application.

Table 3-11: Off-Board Clock Inputs and Outputs

Source

Schematic Signal

Name

I/O Standard

MAX 10 FPGA

Description

J12

USER_CLKIN_P_

MAX10

1.2 V

K21

Single-ended clock input,

or positive terminal for

differential clock inputs

from user GPIO

J12

USER_CLKIN_N_

MAX10

1.2 V

K22

Single-ended clock input,

or negative terminal for

differential clock inputs

from user GPIO

J12

CLKOUT_LVDS_

P

2.5 V

V17

Single-ended clock

output, or positive

terminal for differential

clock output to user

GPIO

J12

CLKOUT_LVDS_

N

2.5 V

W17

Single-ended clock

output, or negative

terminal for differential

clock output to user

GPIO

3-14

Off-Board Clock Input/Output

UG-20006

2016.02.29

Altera Corporation

Board Components

Send Feedback