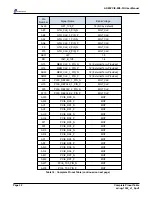

ADM-PCIE-8K5-FH User Manual

Pin

Number

Signal Name

Bank Voltage

AL29

GP1_1V8_P

1.8 (NC by default)

AE7

GTH_CLK_0_PIN_N

MGT_CLK

AE8

GTH_CLK_0_PIN_P

MGT_CLK

AA7

GTH_CLK_1_PIN_N

MGT_CLK

AA8

GTH_CLK_1_PIN_P

MGT_CLK

F9

GTH_CLK_2_PIN_N

MGT_CLK

F10

GTH_CLK_2_PIN_P

MGT_CLK

AK31

H/F

1.8

R11

INIT_B_1V8

1.8

G15

MEM_CLK_0_PIN_N

1.2 (External Term Provided)

G16

MEM_CLK_0_PIN_P

1.2 (External Term Provided)

AN22

MEM_CLK_1_PIN_N

1.2 (External Term Provided)

AM22

MEM_CLK_1_PIN_P

1.2 (External Term Provided)

H9

PCIE_REFCLK_1_PIN_N

MGT_CLK

H10

PCIE_REFCLK_1_PIN_P

MGT_CLK

AT9

PCIE_REFCLK_2_PIN_N

MGT_CLK

AT10

PCIE_REFCLK_2_PIN_P

MGT_CLK

AW3

PCIE_RX0_N

MGT

AW4

PCIE_RX0_P

MGT

AV1

PCIE_RX1_N

MGT

AV2

PCIE_RX1_P

MGT

AU3

PCIE_RX2_N

MGT

AU4

PCIE_RX2_P

MGT

AT1

PCIE_RX3_N

MGT

AT2

PCIE_RX3_P

MGT

AR3

PCIE_RX4_N

MGT

AR4

PCIE_RX4_P

MGT

AP1

PCIE_RX5_N

MGT

AP2

PCIE_RX5_P

MGT

AN3

PCIE_RX6_N

MGT

AN4

PCIE_RX6_P

MGT

AM1

PCIE_RX7_N

MGT

AM2

PCIE_RX7_P

MGT

AW7

PCIE_TX0_PIN_N

MGT

AW8

PCIE_TX0_PIN_P

MGT

Table 14 : Complete Pinout Table (continued on next page)

Page 32

Complete Pinout Table

ad-ug-1342_v1_0.pdf