Operation Theorem

•

35

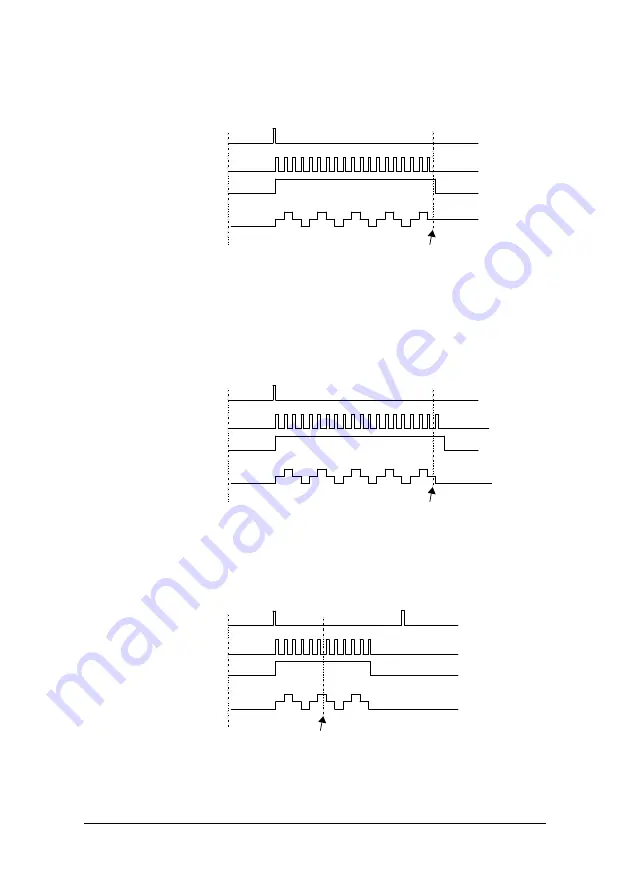

(UC _Counter=4, IC_Counter disabled)

4 update counts, infinite iterations

DAWR

WFG_in_progress

Operation start

Trigger

Output Waveform

0

2

4

stop trigger

Figure 4.2.9 Stop mode I

(Assuming the data in the data buffer are 2V, 4V, 2V, 0V)

(UC _Counter=4, IC_Counter disabled)

4 update counts, infinite iterations

DAWR

WFG_in_progress

Operation start

Trigger

Output Waveform

0

2

4

stop trigger

Figure 4.2.10 Stop mode II

(UC _Counter=4, IC_Counter=3, Trig_Counter>1)

4 update counts, finite iterations

DAWR

WFG_in_progress

Operation start

Trigger

Output Waveform

0

2

4

stop trigger

Figure 4.2.11 Stop mode III

Summary of Contents for NuDAQ DAQ-2500 Series

Page 3: ......

Page 26: ...Operation Theorem 17...