Document number

205065

Version

Rev. N

Issue date

2019-02-04

Sirius OBC and TCM User Manual

Page

32

of

174

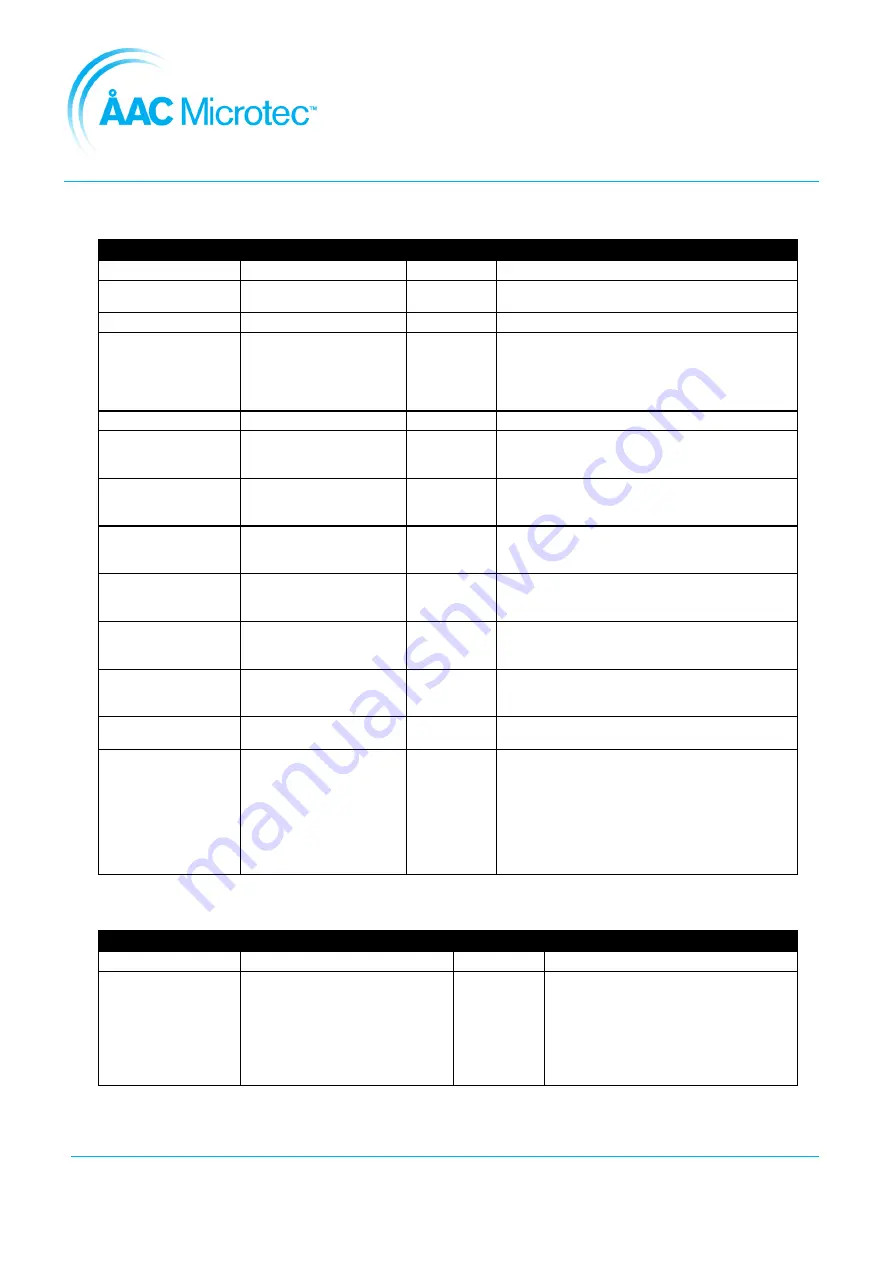

5.3.2.3.1. Status register

Bit position

Name

Direction Description

31:12

RESERVED

11

ERRMAN_PULSEFLG

R/W

Pulse command flag bit is set.

Clear flag by write a ‘1’

10

ERRMAN_POWFLG

R/W

The power loss signal has been set.

9

ERRMAN_MEMCLR

R

The memory cleared signal is set from the

scrubber unit function from the memory

controller. Set when the memory has been

cleared and read by the bootrom to wait for

image.

8

RESERVED

7

ERRMAN_PARFLG

R/W

A previous CPU Register File Parity Error

Reset has been detected

Clear flag by write a ‘1’

6

ERRMAN_MEOTHFLG

R/W

A previous RAM EDAC Multiple Error Reset

has been detected for non-critical data

Clear flag by write a ‘1’

5

ERRMAN_SEOTHFLG

R/W

A previous RAM EDAC Single Error Reset has

been detected for critical data

Clear flag by write a ‘1’

4

ERRMAN_MECRIFLG

R/W

A previous RAM EDAC Multiple Error Reset

has been detected for non-critical data

Clear flag by write a ‘1’

3

ERRMAN_SECRIFLG

R/W

A previous RAM EDAC Single Error Reset has

been detected for critical data

Clear flag by write a ‘1’

2

ERRMAN_WDTFLG

R/W

A previous Watch Dog Timer Reset has been

detected

Clear flag by write a ‘1’

1

ERRMAN_RFLG

R/W

A previous Manual Reset has been detected

Clear flag by write a ‘1’

0

ERRMAN_IFLAG

R/W

Error Manager Interrupt Flag (multiple sources

i.e. read the whole status register)

Read:

‘0’ –

No interrupt pending

‘1’ –

Interrupt pending

Write:

‘0’ –

Ignored

‘1’ –

Clear

5.3.2.3.2. Carry flag register

Bit position

Name

Direction Description

31:8

RESERVED

7

ERRMAN_PARCFLG

R/W

Carry flag set when CPU Register File

Parity Error counter overflow has

occurred

‘0’ –

No CF set

‘1’ –

Counter overflow(Cleared by write

‘1’)