Document number

205065

Version

Rev. N

Issue date

2019-02-04

Sirius OBC and TCM User Manual

Page

31

of

174

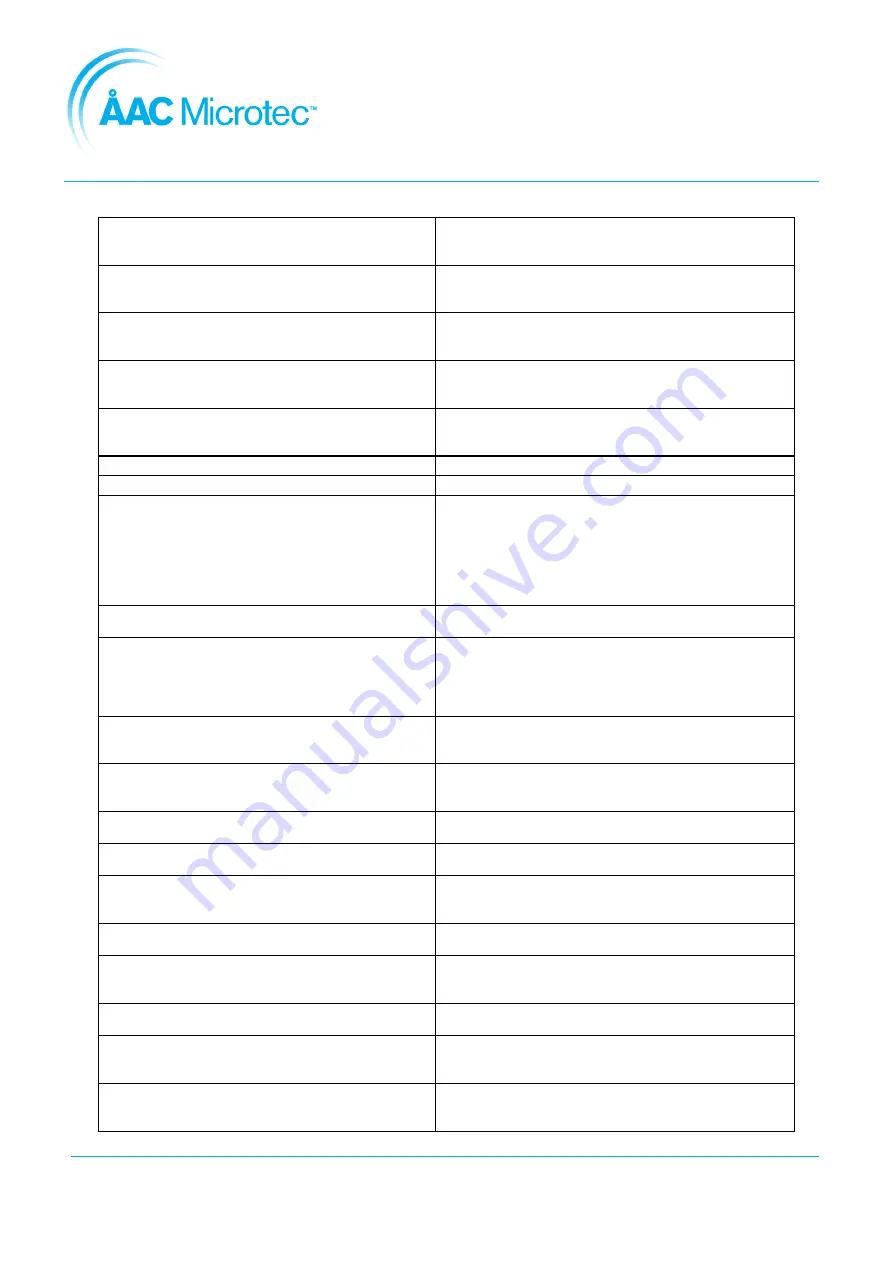

ERRMAN_GET_SYS_SINGLE_ERRCNT_IOCTL

Gets the system flash single error (correctable) error

count.

This register is 4 bit wide and will wrap upon overflow.

ERRMAN_GET_SYS_MULTI_ERRCNT_IOCTL

Gets the system flash multiple error (un-correctable)

error count.

This register is 4 bit wide and will wrap upon overflow.

ERRMAN_GET_MMU_SINGLE_ERRCNT_IOCTL

Gets the mass memory single error (correctable) error

count.

This register is 4 bit wide and will wrap upon overflow.

ERRMAN_GET_MMU_MULTI_ERRCNT_IOCTL

Gets the mass memory multiple error (un-correctable)

error count.

This register is 4 bit wide and will wrap upon overflow.

ERRMAN_GET_POWER_LOSS_ENABLE_IOCTL

Gets the power loss detection enable state.

0 = Power loss detection disabled.

1 = Power loss detection enabled

ERRMAN_SET_SR_IOCTL

Sets the status register, see 5.3.2.3.1

ERRMAN_SET_CF_IOCTL

Sets the carry flag register, see 5.3.2.3.2

ERRMAN_SET_SELFW_IOCTL

Sets the next boot firmware.

0x0: Programmable FW from Power on

0x1: Programmable FW, Backup copy

0x2: Programmable FW, Backup copy

0x3: Safe FW

0x4: Safe FW, Backup copy

0x5: Safe FW, Backup copy

ERRMAN_RESET_SYSTEM_IOCTL

Performs a software reset.

The reset enable state is required to be 1 (On).

ERRMAN_SET_SCRUBBER_IOCTL

Sets the state of the memory scrubber.

1 = On,

0 = Off.

The scrubber is a vital part of keeping the SDRAM free

from errors.

ERRMAN_SET_RESET_ENABLE_IOCTL

Sets the reset enable state.

0 = Soft reset is disabled.

1 = Soft reset is enabled

ERRMAN_SET_WDT_ERRCNT_IOCTL

Sets the watchdog error count register.

The counter width is 4 bits i. e. 15 is the maximum value

that can be written.

ERRMAN_SET_EDAC_SINGLE_ERRCNT_IOCTL

Sets the EDAC single error count.

See 5.3.2.3.3 for register definition.

ERRMAN_SET_EDAC_MULTI_ERRCNT_IOCTL

Sets the EDAC multiple error count register.

See 5.3.2.3.4 for register definition.

ERRMAN_SET_CPU_PARITY_ERRCNT_IOCTL

Sets the CPU Parity error count register.

The counter width is 4 bits i. e. 15 is the maximum value

that can be written.

ERRMAN_SET_SYS_SINGLE_ERRCNT_IOCTL

Sets the system flash single (correctable) error counter.

This register is 4 bit wide.

ERRMAN_SET_SYS_MULTI_ERRCNT_IOCTL

Sets the system flash multiple (un-correctable) error

counter.

This register is 4 bit wide.

ERRMAN_SET_MMU_SINGLE_ERRCNT_IOCTL

Sets the mass memory single (correctable) error counter.

This register is 4 bit wide.

ERRMAN_SET_MMU_MULTI_ERRCNT_IOCTL

Sets the mass memory multiple (un-correctable) error

counter.

This register is 4 bit wide.

ERRMAN_SET_POWER_LOSS_ENABLE_IOCTL

Sets the power loss enable state.

0 = Power loss detection disabled.

1 = Power loss detection enabled