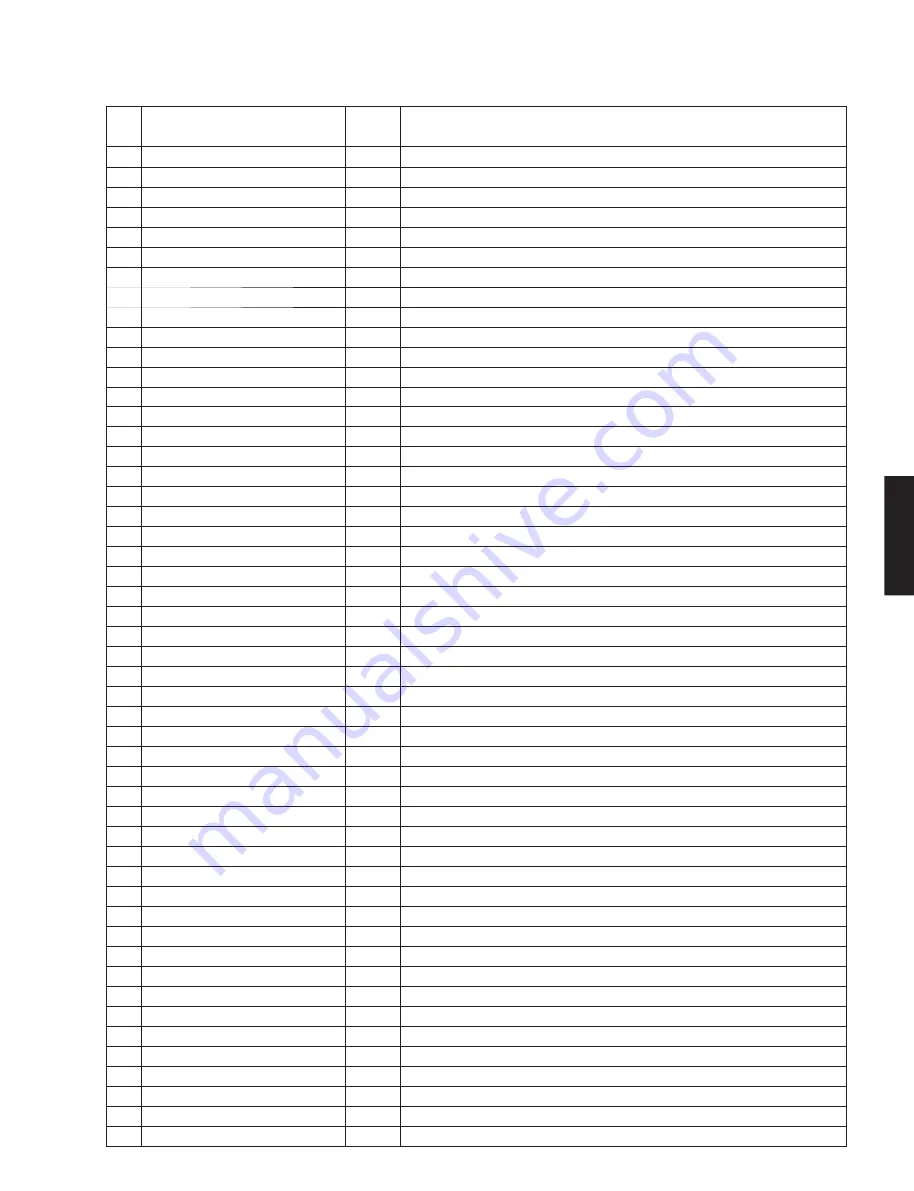

No.

Function Name

(P.C.B.)

I/O

Detail of Function

1

VSS

2

AHCLKX0/AHCLKX2

IO

McASP0 and McASP2 transmit master clock

3

AMUTE0

IO

McASP0 mute output

4

AMUTE1

IO

McASP1 mute output

5

AHCLKX1

IO

McASP1 transmit master clock

6

VSS

7

ACLKX1

IO

McASP1 transmit bit clock

8

CVDD

9

ACLKR1

IO

McASP1 receive bit clock

10

DVDD

11

AFSX1

IO

McASP1 transmit frame Sync (L/R clock)

12

AFSR1

IO

McASP1 receive frame Sync (L/R clock)

13

VSS

14

RESET

IO

Device reset pin

15

VSS

16

CVDD

17

CLKIN

IO

Alternate clock input (3.3-V LVCMOS input)

18

VSS

19

TMS

IO

Test mode select

20

CVDD

21

TRST

IO

Test reset

22

OSCVSS

PWR

Oscillator Vss tap point (for filter only)

23

OSCIN

IO

1.2-V oscillator input

24

NC

O

25

OSCVDD

PWR

Oscillator 1.2-V Vpp tap point (for filter only)

26

VSS

27

PLLHV

PWR

PLL 3.3-V supply input (requires external filter)

28

TDI

IO

Test data in

29

TDO

OZ

Test data out

30

VSS

31

DVDD

32

EMU[0]

IO

Emulation pin 0

33

CVDD

34

EMU[1]

IO

Emulation pin 1

35

TCK

IO

Test clock

36

Ground(Vss)

37

EM_CAS

O

SDRAM column address strobe

38

EM_WE

O

SDRAM write enable

39

EM_WE_DQM[0]

O

Write enable or byte enable for EM_D [7:0]

40

VSS

41

EM_D[7]

IO

EMIF data bus [lower 16-bits]

42

DVDD

43

EM_D[6]

IO

EMIF data bus [lower 16-bits]

44

CVDD

45

EM_D[5]

IO

EMIF data bus [lower 16-bits]

46

EM_D[4]

IO

EMIF data bus [lower 16-bits]

47

VSS

48

EM_D[3]

IO

EMIF data bus [lower 16-bits]

49

EM_D[2]

IO

EMIF data bus [lower 16-bits]

50

DVDD

69

RX-V475/HTR-4066/RX-V500D

RX-V475/HTR-4066/

RX-V50

0D

Содержание RX-V500D

Страница 9: ...RX V500D A model RX V500D B G models 9 RX V475 HTR 4066 RX V500D RX V475 HTR 4066 RX V500D ...

Страница 132: ... CONFIGURING THE SYSTEM SETTINGS RX V475 HTR 4066 RX V500D 133 ...

Страница 133: ... システム設定を変更する RX V475 HTR 4066 RX V500D 134 ...

Страница 146: ...147 RX V475 HTR 4066 RX V500D RX V475 HTR 4066 RX V500D MEMO ...

Страница 147: ...RX V475 HTR 4066 RX V500D ...