HDMI 1.4/2.0 TX Subsystem

45

PG235 October 4, 2017

Chapter

3:

Designing with the Subsystem

each pixel twice. When the video is sent out by the HDMI 1.4/2.0 Transmitter Subsystem, it

is sent as two fields of 1440x240 @ 30Hz video.

Clocking

The

S_AXI_CPU_IN

,

VIDEO_OUT

, and

AUDIO_OUT

can be run at their own clock rate. The

HDMI link interfaces and native video interface also run at their own clock rate. Therefore,

five separate clock interfaces are provided called

s_axi_cpu_aclk

,

s_axis_video_aclk

,

s_axis_audio_aclk

,

link_clk

, and

video_clk

respectively.

The audio streaming clock must be greater than or equal to 128 times the audio sample

frequency. Because audio clock regeneration is not part of the HDMI TX subsystem, you

must provide an audio clock to the application. This can be achieved by using an internal

PLL or external clock source.

IMPORTANT:

The AXI4-Lite CPU clock must run at 100 Mhz.

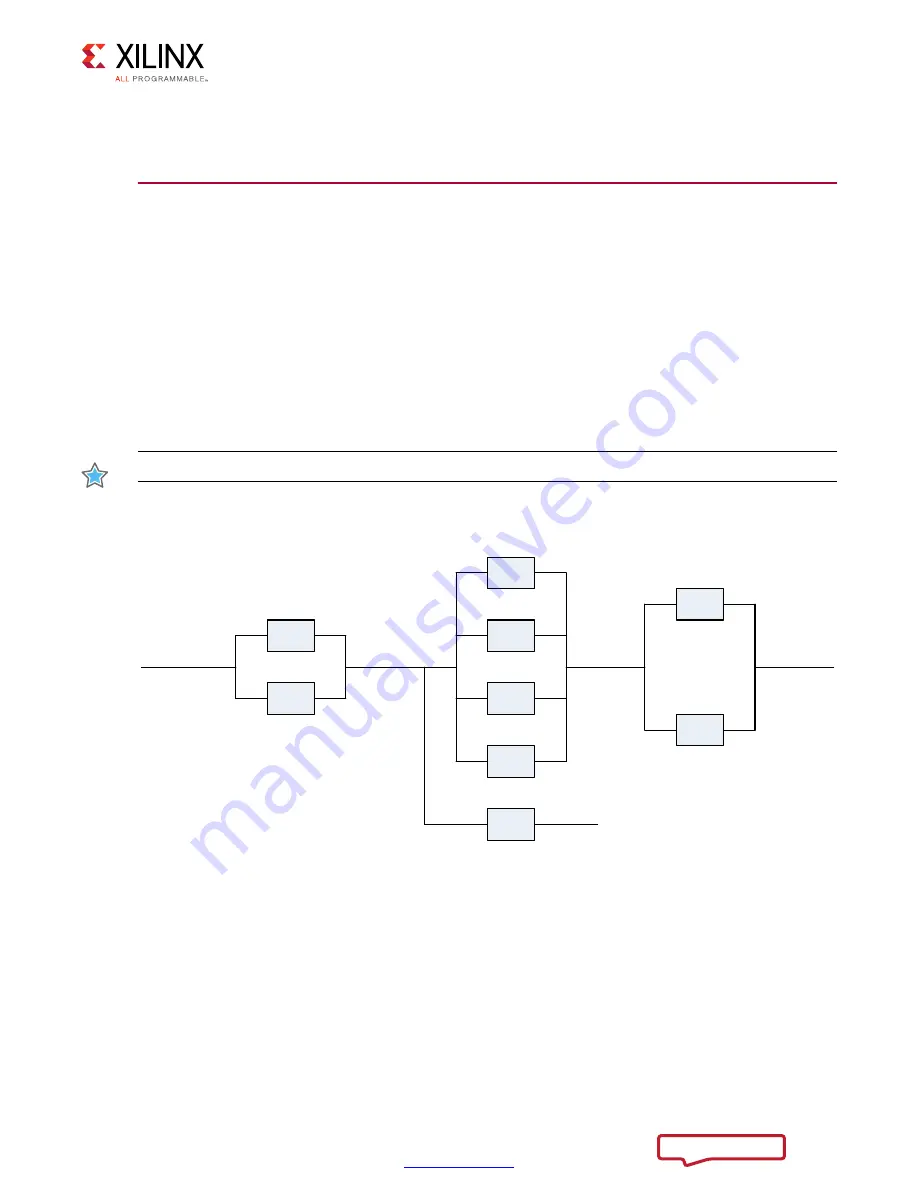

The HDMI clock structure is illustrated in

and

X-Ref Target - Figure 3-10

Figure

3

‐

10:

HDMI Clocking Structure

Data rate

< 3.4 Gbps

*1

Data rate

>3.4 Gbps

*4

TMDS

clock

Data

clock

/4

10 bpc

/1.25

8 bpc

/1

12 bpc

/1.5

16 bpc

/2

Pixel

clock

Dual

/2

Quad

/4

Video

clock

Link

clock