User's Manual l TQMa8XxS UM 0101 l © 2022, TQ-Systems GmbH

Page 34

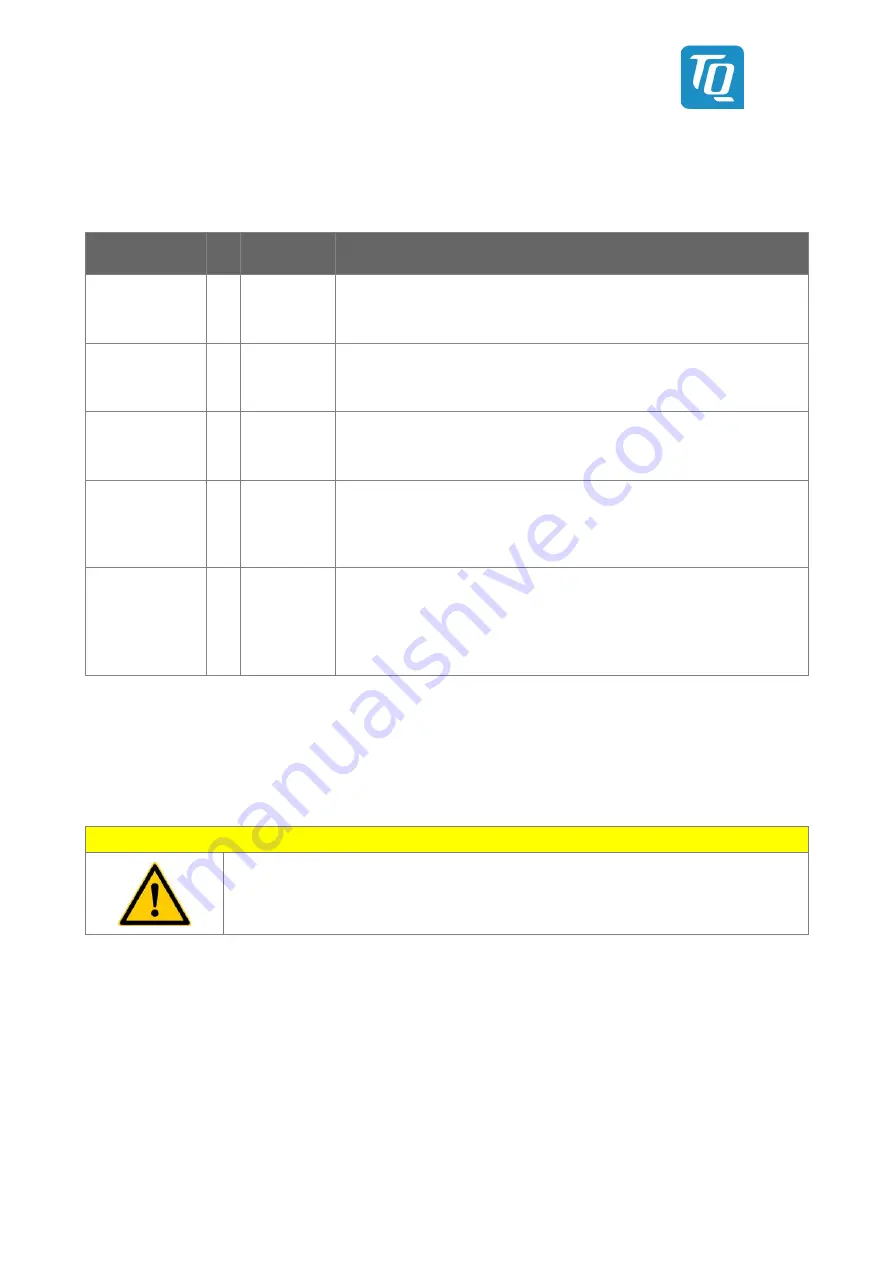

A part of the control signals between PMIC and CPU is also available at the SMARC pins. A more detailed signal description can

be found in the following table:

Table 20:

Provided PMIC signals

SMARC-Pin

I/O

Power

domain

Remark

RESET_IN#

I

V_1V8_ANA

•

reset input of the i.MX 8X via diode to POR_B of the CPU (pull-up to

module); low active

RESET_OUT#

O

V_1V8_ANA

•

reset output of the PMIC (pull-down to module)

I2C_PM_CK

I2C_PM_DAT

I/O V_1V8_ANA

•

dedicated PMIC interface

•

can be used for further power management on mainboard

•

see I2C interfaces

CARRIER_PWR_ON

O

V_1V8_ANA

•

enable signals of the power supply on carrier

•

output of the PMIC power monitor

•

has pull-up on module

•

see data sheet PMIC

VIN_PWR_BAD#

I

VDD_IN

•

status module voltage supply from Carrier

•

enable signal for PMIC (high-active), buck-boost and linear regulator

•

is activated by default when V_3V3_IN is switched on

•

to activate: float or connect to 3.3 V

•

to deactivate: connect to GND

The properties and functions of the pins and signals are described in the data sheets res. reference manuals of the PMIC (4) and

the CPU (1)(2).

PMICs in die revision C1 are used, which use module-specific OTP programming. The program data was created with the tool

"OTP-Request-Form" from NXP.

According to the specification, the PMIC can be configured via the PMIC_I2C interface after the boot of the system.

Attention: Malfunction or destruction

The PMIC can be controlled via the dedicated i.MX 8X I

2

C bus (PMIC_I2C).

Improper PMIC programming may cause the i.MX 8X or other peripherals on the TQMa8XxS

to operate outside their specification.

This can lead to malfunction, deterioration or destruction of the TQMa8XxS.