SM320F2812-HT

www.ti.com

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

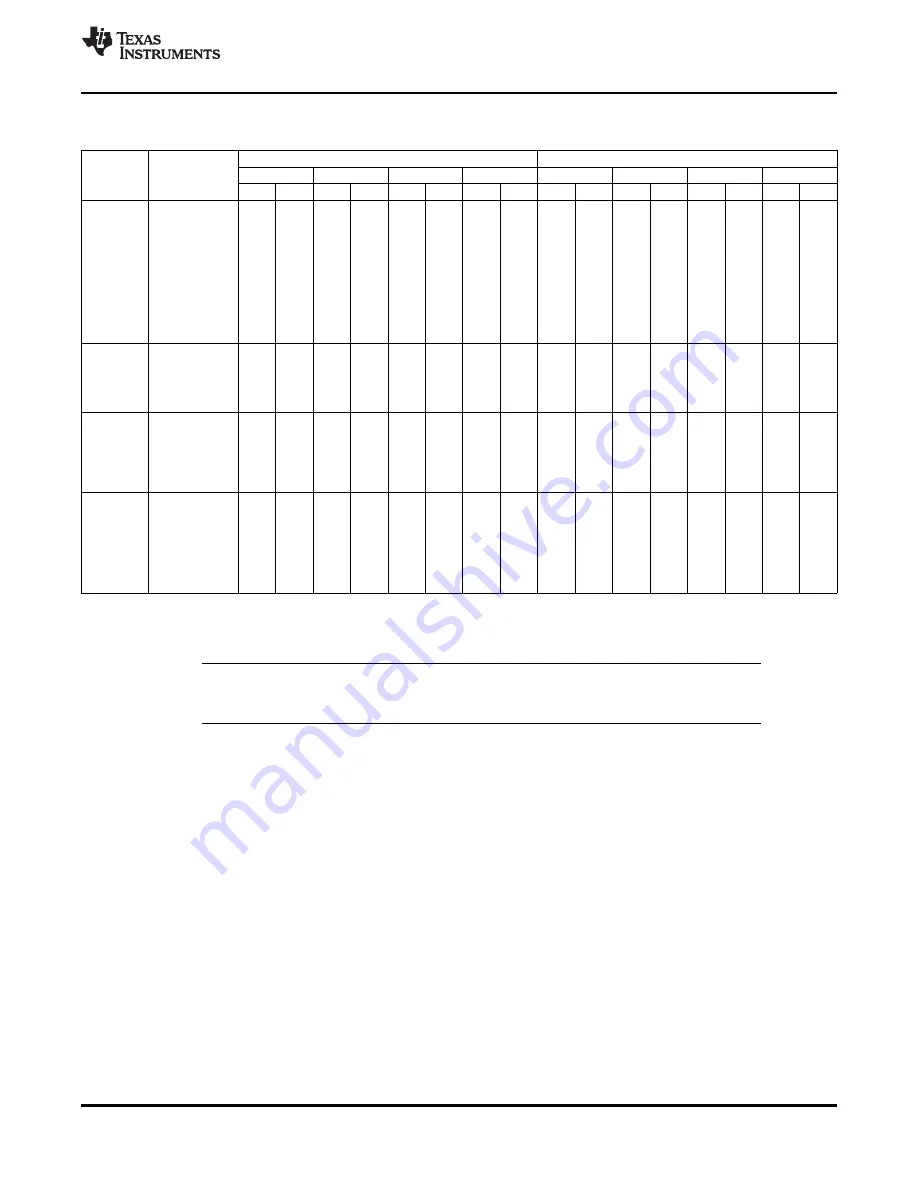

6.4

Current Consumption by Power-Supply Pins Over Recommended Operating

Conditions During Low-Power Modes at 150-MHz SYSCLKOUT

T

A

=

–

55

°

C to 125

°

C

T

A

= 220

°

C

MODE

TEST CONDITIONS

I

DD

I

DDIO

I

DD3VFL

I

DDA

(1)

I

DD

I

DDIO

I

DD3VFL

I

DDA

(1)

TYP

MAX

(2)

TYP

MAX

(2)

TYP

MAX

(2)

TYP

MAX

(2)

TYP

MAX

TYP

MAX

TYP

MAX

TYP

MAX

All peripheral clocks

are enabled. All

PWM pins are

toggled at 100 kHz.

Data is continuously

transmitted out of the

Operational

SCIA, SCIB, and

195 mA 230 mA

15 mA

30 mA

40 mA

45 mA

40 mA

50 mA

275 mA 330 mA

17 mA

30 mA

45 mA

50 mA

40 mA

52 mA

CAN ports. The

hardware multiplier is

exercised.

Code is running out

of flash with 5

wait-states.

–

Flash is powered

down

–

XCLKOUT is turned

IDLE

125 mA 150 mA

5 mA

10 mA

2

μ

A

4

μ

A

1

μ

A

35

μ

A

200 mA

10 mA

56

μ

A

100

μ

A

320

μ

A

450

μ

A

off

–

All peripheral clocks

are on, except ADC

–

Flash is powered

down

–

Peripheral clocks

STANDBY

are turned off

5 mA

10 mA

5

μ

A

20

μ

A

2

μ

A

4

μ

A

1

μ

A

35

μ

A

27 mA

40 mA

160

μ

A

200

μ

A

56

μ

A

100

μ

A

320

μ

A

450

μ

A

–

Pins without an

internal PU/PD are

tied high/low

–

Flash is powered

down

–

Peripheral clocks

are turned off

HALT

–

Pins without an

70

μ

A

5

μ

A

20

μ

A

2

μ

A

4

μ

A

1

μ

A

35

μ

A

9.8 mA

160

μ

A

200

μ

A

56

μ

A

100

μ

A

320

μ

A

450

μ

A

internal PU/PD are

tied high/low

–

Input clock is

disabled

(1)

I

DDA

includes current into V

DDA1

, V

DDA2

, V

DD1

, AV

DDREFBG

, and V

DDAIO

pins.

(2)

MAX numbers are at 125

°

C, and max voltage (V

DD

= 2.0 V; V

DDIO

, V

DD3VFL

, V

DDA

= 3.6 V).

xxx

NOTE

HALT and STANDBY modes cannot be used when the PLL is disabled.

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Electrical Specifications

87

Submit Documentation Feedback

Product Folder Link(s):

SM320F2812-HT

Содержание SM320F2812-HT Data

Страница 152: ......