2P

1P

1N

4P

3P

BAT

VSS

VSS

VSS

VSS

GND

SRP

SRN

6P

5P

20.0

R3

TP14

100

R27

100

R28

TP12

0.001

R30

t

°

RT1

VC6

VC5

VC4

VC3

VC2

VC1

SRP

SRN

TS2

PACK

DSG

PCHG

CHG

FUSE

NT1

Net-Tie

7P

100

R1

TP18

TP19

BAT-

GND

20.0

R2

TP2

VSS

PDSG

VC0

VC7

REG1

2.2uF

C25

BAT-

1P

2P

3P

4P

5P

6P

TP5

TP10

VSS

GND

TP15

0.47uF

C3

4

1

3

2

S1

0

R15

DNP

VSS

GND

TP16

VSS

GND

TP17

PGND

LD

1

2

3

J7

10k

R29

TP11

TS1

TS2

20.0

R4

20.0

R7

20.0

R8

20.0

R11

20.0

R12

20.0

R13

CHG

DSG

PACK

LD

PCHG

PDSG

FUSE

VSS

VSS

10k

R20

TP13

TP4

VSS

TP7

REG1

VSS

Input

72V 6A

7P

CD

WAKE

4

1

3

2

S2

RESET

TP3

BREG

REGIN

LD

41

VC1

15

SDA

27

VC16

48

CHG

45

VC3

13

VC5

11

VC7

9

VC9

7

VC11

5

VC13

3

VC15

1

FUSE

38

BREG

37

REG18

24

HDQ

28

SCL

26

ALERT

25

VC0

16

VSS

17

SRP

18

NC

19

SRN

20

NC

44

TS1

21

TS2

22

TS3

23

DSG

43

BAT

47

CFETOFF

29

DFETOFF

30

DCHG

31

DDSG

32

RST_SHUT

33

REG2

34

REG1

35

REGIN

36

PACK

42

PDSG

39

PCHG

40

VC2

14

VC4

12

VC6

10

VC8

8

VC10

6

VC12

4

VC14

2

CP1

46

bq76952PFBT

U1

VC14

VC13

VC12

VC11

VC10

VC9

VC8

VC15

VC16

20.0

R16

20.0

R14

20.0

R17

20.0

R18

20.0

R19

20.0

R21

20.0

R22

20.0

R23

20.0

R24

13P

12P

11P

15P

14P

16P

9P

8P

10P

8P

9P

10P

11P

12P

13P

14P

15P

16P

t

°

RT2

VSS

VSS

TP8

REG2

VSS

CFETOFF

HDQ

ALERT

SDA

SCL

TS2

REGIN

REG1

VSS

VSS

REG1

DFETOFF

DDSG

DCHG

VSS

VSS

DDSG

DCHG

DFETOFF

EXTTS2

1

2

3

J6

10k

R25

REG1

VSS

TP1

DNP

TP9

DNP

RST_SHUT

5

4

1

2

3

6

J5

EXTTS2

RST_SHUT

CFETOFF

CFETOFF

CFETOFF

0.01uF

C20

1uF

C12

0.1uF

C28

5

4

1

2

3

J2

REG2

REG2

BAT+

100k

R26

100V

D1

1

3

2

,4 Q1

FCX495TA

220

R9

220

R5

220

R6

DNP

220

R10

DNP

1uF

C15

1

2

3

4

5

1

2

3

4

5

J3

1

2

3

4

5

6

1

2

3

4

5

6

J4

1

2

3

4

5

6

1

2

3

4

5

6

J1

100V

D2

1uF

C1

VSS

100pF

C2

0.01uF

C26

DNP

100pF

C27

TP6

VSS

1uF

C71

22nF

C13

220nF

C24

220nF

C23

220nF

C22

220nF

C21

220nF

C19

220nF

C18

220nF

C11

220nF

C17

220nF

C16

220nF

C14

220nF

C10

220nF

C9

220nF

C8

220nF

C7

220nF

C6

220nF

C5

220nF

C4

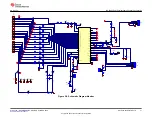

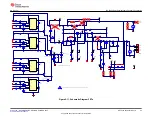

Figure 5-9. Schematic Diagram Monitor

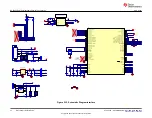

BQ76952EVM Circuit Module Physical Construction

SLUUC33A – NOVEMBER 2019 – REVISED OCTOBER 2020

BQ76952 Evaluation Module

41

Copyright © 2020 Texas Instruments Incorporated