TPMC533 User Manual Issue 1.0.1

Page 28 of 107

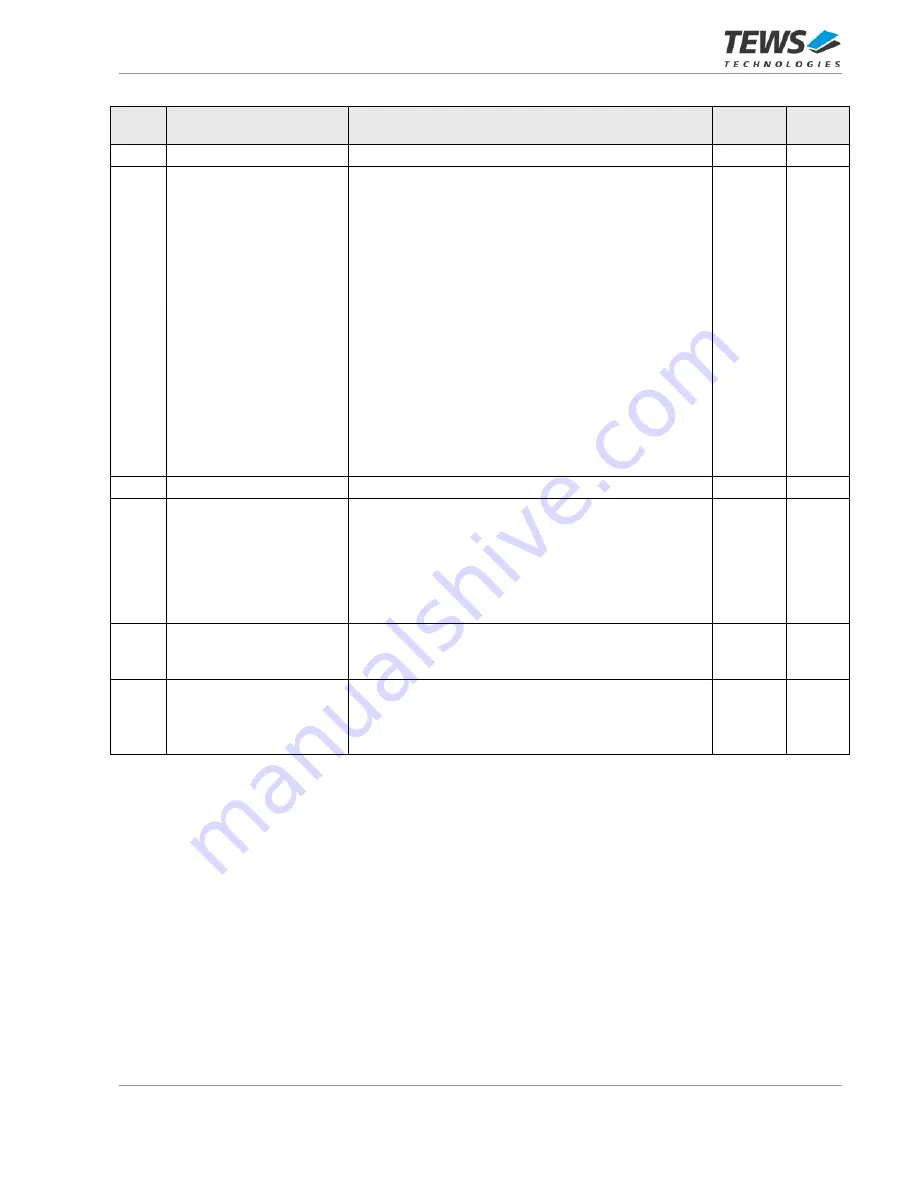

3.2.1.3.2

ADC Sequencer Status Register (0x124)

Bit

Symbol

Description

Access

Reset

Value

31:23

-

Reserved

-

-

22:20

WR_DMA_TERM

DMA Buffer Termination

After a DMA Buffer was terminated, depending on which

bits are set in this array, the reason(s) for the termination

are indicated.

These bits are automatically cleared when a new DMA

Buffer is provided by writing to the DMA Buffer Length

Register.

Bit 22: Error

The Input Unit operation is stopped before the desired

Number of Conversions has been performed because a

Conversion Error or a FIFO Overflow occurred.

Bit 21: Block/Frame End

The desired number of samples (configured in the

Number of Conversions Register) has been written to

DMA Buffers.

Bit 20: Buffer End

The end of the DMA Buffer was reached (the DMA Buffer

is full). A new DMA Buffer must be provided.

R

000

19

-

Reserved

-

-

18

WR_DMA_ERR

DMA Error

A PCI Master Abort occurred because the addressed PCI

Target did not respond or a PCI Target Abort occurred

because the addressed PCI Target detected a fatal error.

In case of an error, the DMA Controller operation is

automatically stopped.

This bit is cleared when the DMA Controller is disabled.

R

0

17

WR_DMA_BUSY

DMA Busy

Indicates that the DMA Controller is currently busy

(active).

R

0

16

WR_DMA_IDLE

DMA Idle

Indicates that the DMA Controller is currently in Idle State.

A DMA transfer may be started (a DMA buffer may be

provided) by writing to the DMA Buffer Length Register.

R

0