TPMC533 User Manual Issue 1.0.1

Page 24 of 107

3.2.1.2.3

ADC Data Registers (0x038, 0x03C, 0x040, 0x044, 0x07C, 0x080, 0x084, 0x088,

0x0C0, 0x0C4, 0x0C8, 0x0CC, 0x104, 0x108, 0x10C and 0x110)

These registers are intended to be used for ADCs operating in Manual Mode (not for Sequencer Mode).

To accelerate data access, each ADC Data Register holds two ADC channel values.

The ADC Data Registers always hold sampled data of the latest conversion.

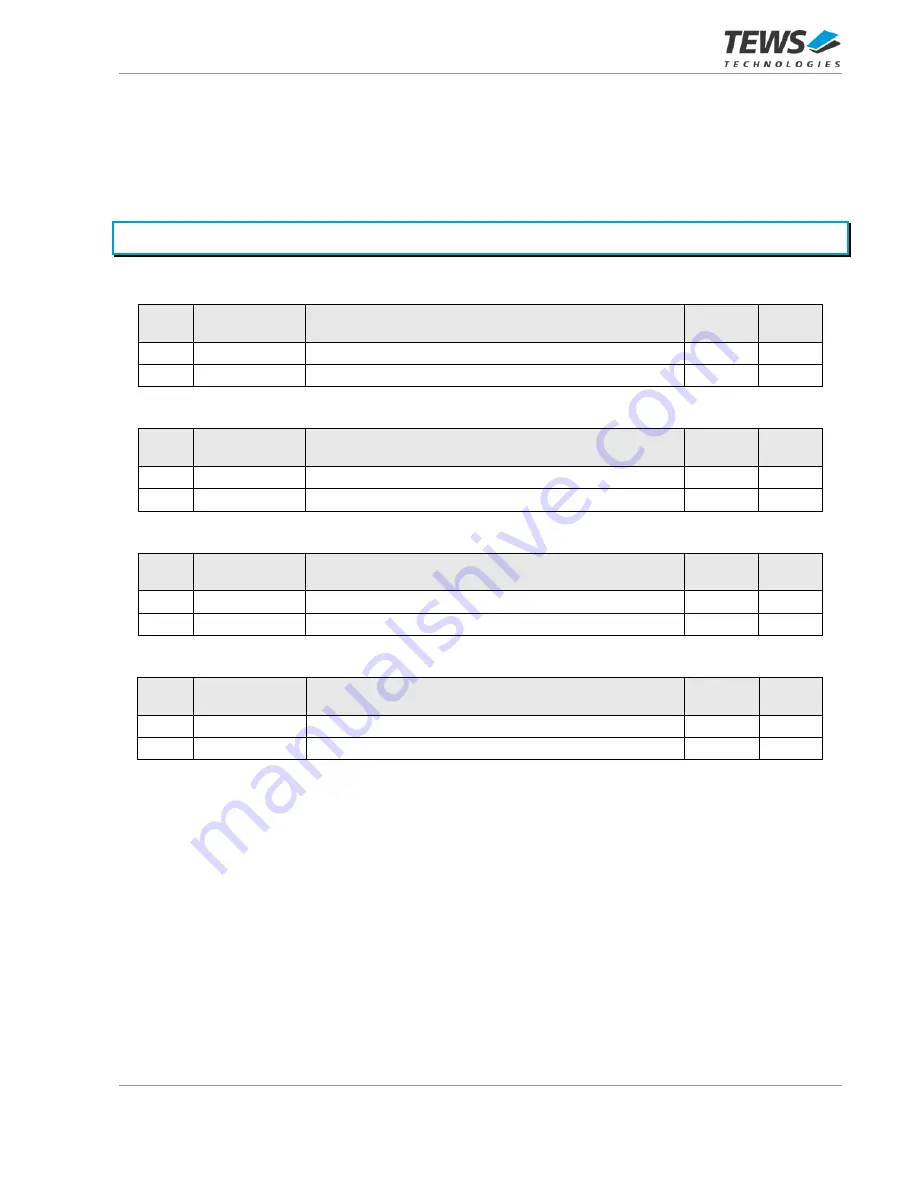

Bit

Symbol

Description

Access

Reset

Value

31:16

ADCx_DATA_B

ADC Data ADC Channel B

R/W

0x0000

15:0

ADCx_DATA_A

ADC Data ADC Channel A

R/W

0x0000

Table 3-16: ADC Data Register A & B

Bit

Symbol

Description

Access

Reset

Value

31:16

ADCx_DATA_D ADC Data ADC Channel D

R/W

0x0000

15:0

ADCx_DATA_C ADC Data ADC Channel C

R/W

0x0000

Table 3-17: ADC Data Register C & D

Bit

Symbol

Description

Access

Reset

Value

31:16

ADCx_DATA_F

ADC Data ADC Channel F

R/W

0x0000

15:0

ADCx_DATA_E

ADC Data ADC Channel E

R/W

0x0000

Table 3-18: ADC Data Register E & F

Bit

Symbol

Description

Access

Reset

Value

31:16

ADCx_DATA_H

ADC Data ADC Channel H

R/W

0x0000

15:0

ADCx_DATA_G ADC Data ADC Channel G

R/W

0x0000

Table 3-19: ADC Data Register G & H