-

--

2

2

/

7

e

g

a

P

-

--

CUnet Family MKY44-IO32A

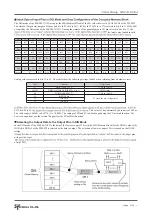

Pin Functions of the DIO mode

Pin name

Pin number

Logic

I/O

Function

DEC1UF

3

--

--

Connect a capacitor whose ef

fective capacitance is at least 1 μF and a 0.1 μF ceramic capacitor

for high frequency bypass in parallel between this pin and V

SS

. Or connect a laminated ceramic

capacitor of around 2.2 μF with the property that capacitance reduction is about 20% even in

DC bias.

#Reset

6

Negative I/O The hardware reset input pin of MKY44-IO32A. Right after power is turned on or when the

user intentionally resets the hardware, Low should be retained for at least 200 μs.

IOSWAP

7

Positive

I

Input pin for the setting that inverts the “input” or “output” status of the 32 general-purpose I/

O pins determined by the settings of IOS0 and IOS1. If the Low-level is set when this pin is

High-level, “input” will be inverted to “output,” and vice versa. The setting status of this pin is

read when returning from a hardware reset.

XTAL4i

XTAL4o

10,11

--

--

Pins to connect a crystal oscillator. Connect a 4 MHz crystal oscillator between these pins.

Connect 20 pF ceramic capacitors between these pins and V

SS

. Connect them near the pins.

DIP_ON

15

Positive

O

Connect this pin with pin DIP_ON of the ST44SW. For more information about the ST44SW,

refer to the ST44SW User’s Manual.

DIP_RX

17

Positive

I

Connect this pin with pin DIP_TX of the ST44SW. For more information about the ST44SW,

refer to the ST44SW User’s Manual.

Io30 to Io37

16

18 to 22

24, 25

Positive

I/O

Pins corresponding to bits 24 to 31 among the 32 bits of general-purpose I/O pins.

Leave this pin open when not in use.

Io00 to Io07

27 to 34

Positive

I/O

Pins corresponding to bits 0 to 7 among the 32 bits of general-purpose I/O pins.

Leave this pin open when not in use.

Io10 to Io17

35 to 42

Positive

I/O

Pins corresponding to bits 8 to 15 among the 32 bits of general-purpose I/O pins.

Leave this pin open when not in use.

Io20 to Io27

43 to 46

59 to 62

Positive

I/O

Pins corresponding to bits 16 to 23 among the 32 bits of general-purpose I/O pins.

Leave this pin open when not in use.

ChipMode

26

Positive

I

Pin to set the mode of the MKY44-IO32A. To use it as described in this data sheet, be sure to

retain the High-level by connecting to Vdd.

DONA

47

Positive

O

This pin retains the High-level during the DONA (DO Not Arrival) state.

It is at Low-level at other times.

STB2

48

Positive

O

Outputs a High-level pulse when reading in the status of the general-purpose input pins.

The MKY44-IO32A reads in the status of the general-purpose input pins while this pin is High.

STB1

50

Positive

O

Outputs a High-level pulse when updating the status of the general-purpose output pins.

The MKY44-IO32A updates the status of the general-purpose output pins while this pin in High.

IOS0

51

Positive

I

Pins to set the “input” or “output” status of the 32 general-purpose I/O pins. Using a

combination of High-level and Low-level input to this pin, “input” or “output” is set for the 32

general-purpose I/O pins. The setting status of these two pins (IOS0 and IOS1) is read when

returning from a hardware reset.

IOS1

52

#MCARE

53

Negative

O

A pin to output the MCARE signal, which is a standard function of CUnet. This pin outputs the

Low-level for about 50 ms, when the MCARE signal occurs and when it returns from hardware

reset.

#LCARE

54

Negative

O

A pin to output the LCARE signal, which is a standard function of CUnet. This pin outputs the

Low-level for about 50 ms, when the LCARE signal occurs and when it returns from hardware

reset.

It is recommended to connect orange color LED indicating a gentle warning to this pin.

#MON

55

Negative

O

A pin to output the MON signal, which is a standard function of CUnet. This pin retains Low-

level while a link has been established with another CUnet devices for at least 3 consecutive

cycles.

It is recommended to connect green color LED indicating a stable operation to this pin.

CU_TXD

56

Positive

O

Output pin to send CUnet packets.

Connect this pin to a drive input pin such as of a driver.

CU_TXE

57

Positive

O

A pin to output the High-level while CUnet packets are output.

Connect this pin to the enable input pin of the driver.

CU_RXD

58

Positive

I

A pin to input CUnet packets.

Connect this pin to the output pin of the receiver.

Vdd

1, 2, 4, 23

--

--

Power pin. Supply 3.3 V.

Vss

5, 9, 12

--

--

Power pin. Connected to 0 V.

N.C.

8, 13, 14,

49, 63, 64

--

--

Do not connect to other signals; keep them open.