STR-DN1000

STR-DN1000

19

19

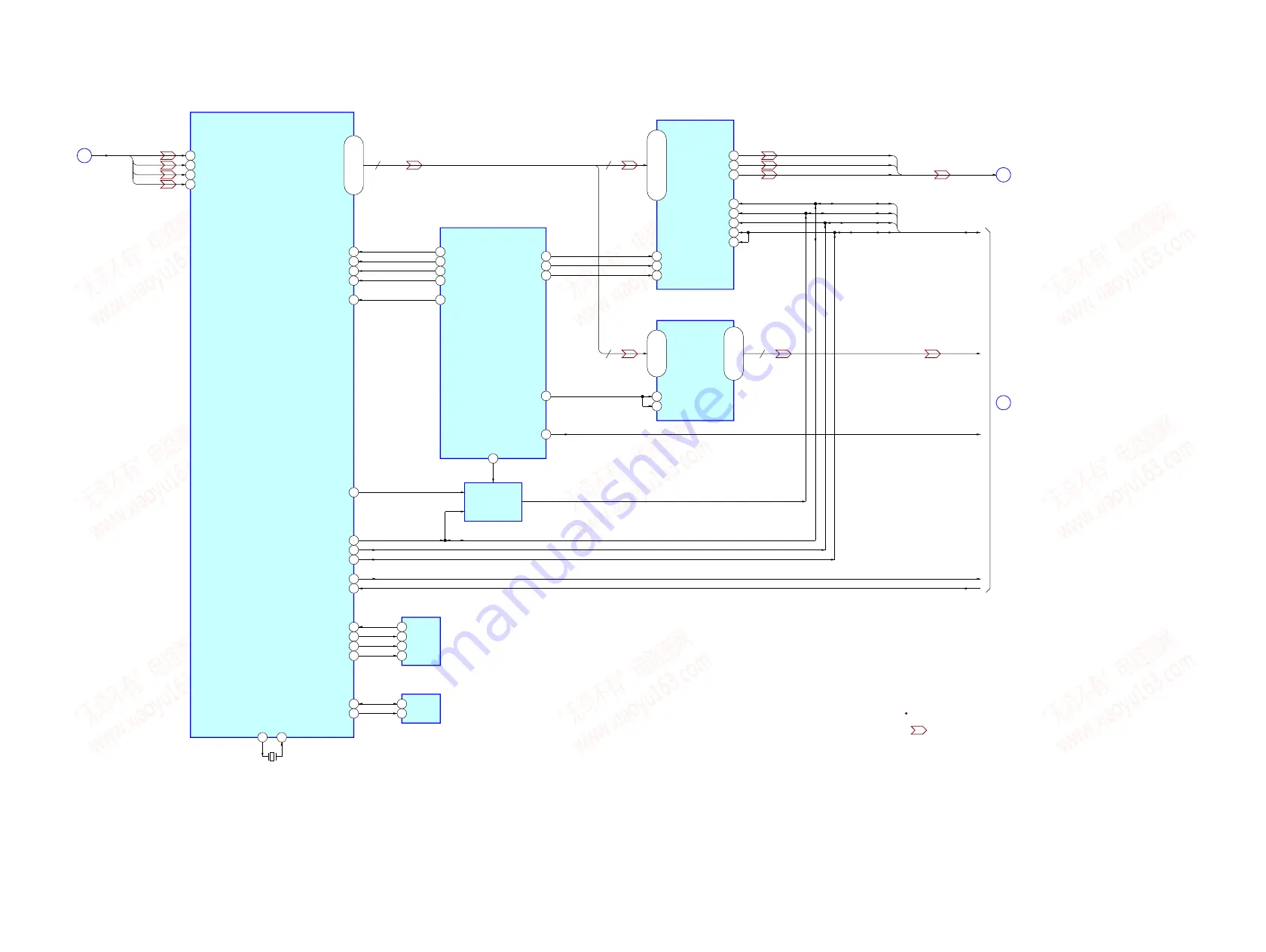

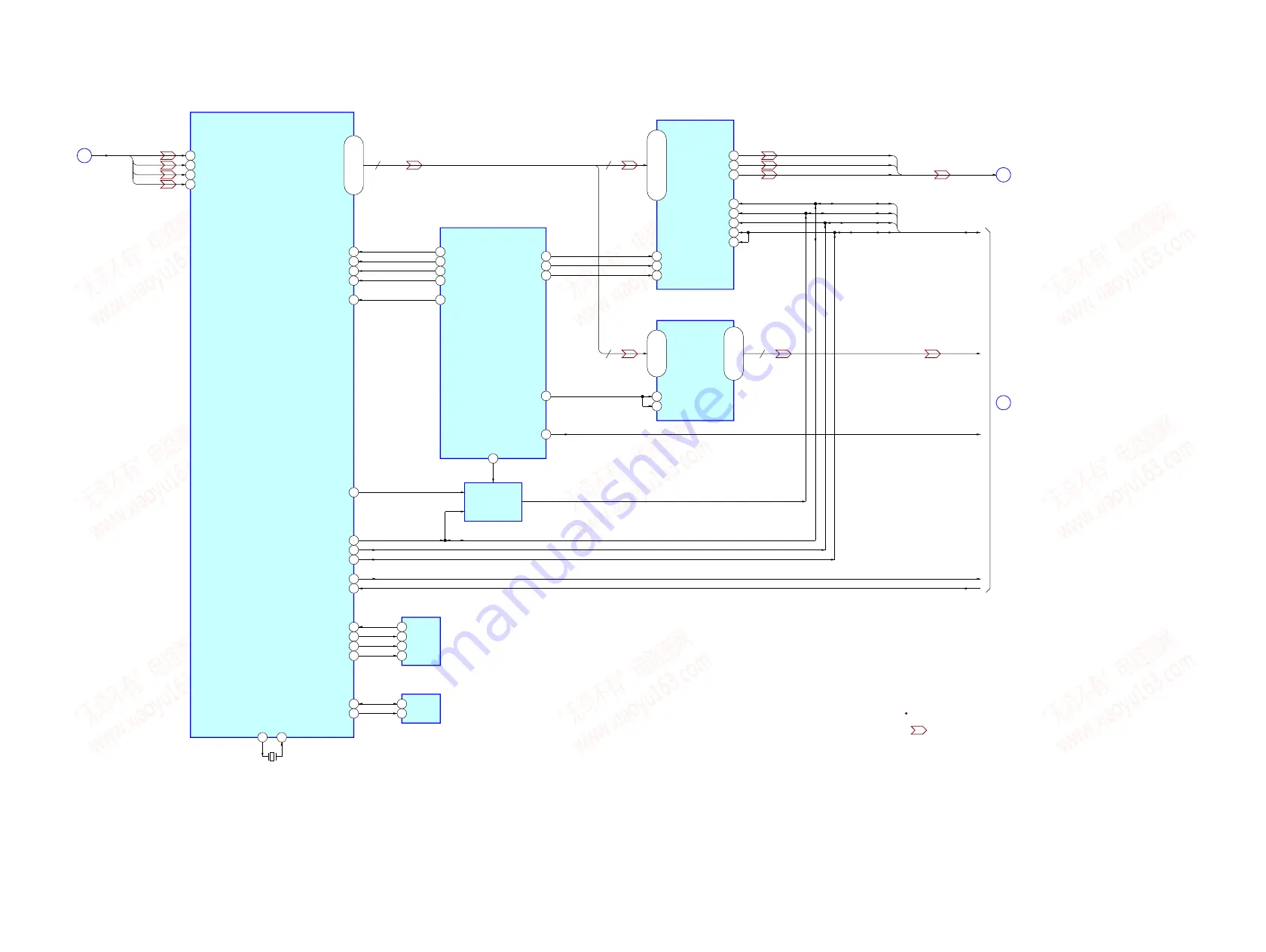

5-3. BLOCK DIAGRAM - VIDEO Section -

: VIDEO

SIGNAL PATH

DAC_SDA/N1 46

DAC_SCL/N1 47

DAC_RESET 19

GPIO1/N1 20

HSYNC_SEL/N1

22

UPDATE SW/N1 9

SYSTEM CONTROLLER

IC2018 (2/5)

VIDEO CONTROLLER

IC3201

OVS/VOP_VS 69

DHS/VOP_HS 68

HOST_SDAT/UART_DO/JTAG_MODE 23

HOST_SCLK/UART_DI/JTAG_CLK 22

ROM_SDI/ROM_WEn 109

ROM_SDO/A16/OPM2 108

ROM_SCLK/A17 107

ROM_SCSn/ROM_CSn 106

102 – 99, 96 – 87,

84 – 75

Y/G 39

CB/R 38

CR/B 37

D/A CONVERTER

IC3850

C7 – C0,

Y7 – Y0,

S7 – S0

B1P

221

C1P

223

A1P

219

A4P

249

W

Y, PB/CB,

PR/CR, V

PR/CR

V

Y

PB/CB

30 – 26, 18 – 16, 13, 12,

9 – 4, 62 – 58, 55 – 53

24

24

24

24

FLI_DATA/N1

6

FLI_CLK/N1

7

FLI STBY/N1

10

FLI_RESET/N1

23

GPIO2/N1

24

GPIO10/SIPC_SDAT/A20

PD23/B7/GPIO48 – PD20/B4/GPIO45,

CH0N_LV_O/B3, CH0P_LV_O/B2,

CH1N_LV_O/B1, CH1P_LV_O/B0,

CH2N_LV_O/G7, CH2P_LV_O/G6,

CLKN_LV_O/G5, CLKP_LV_O/G4,

CH3N_LV_O/G3, CH3P_LV_O/G2,

CH0N_LV_E/G1, CH0P_LV_E/G0,

CH1N_LV_E/R7, CH1P_LV_E/R6,

CH2N_LV_E/R5, CH2P_LV_E/R4,

CLKN_LV_E/R3, CLKP_LV_E/R2,

CH3N_LV_E/R1, CH3P_LV_E/R0

42

GPIO09/SIPC_SCLK/A19 41

LBADC_IN1 2

RESETn 8

GPIO34 156

SDA

21

SCLK

22

RESET

33

BUS SWITCH

IC3523

1A1 – 1A12,

2A1 – 2A12

2 – 7, 9 – 16,

18, 20 – 28

1B1 – 1B12,

2B1 – 2B12

54 – 50, 48 – 39,

37 – 29

1OE

56

2OE

55

P_HSYNC 23

P_VSYNC 24

CLKIN_A 32

P_BLANK 25

S_BLANK 48

HSYNC

SELECT

IC3204, 3205, 3206

DEN/VOP_FLD 67

DCLK/VOP_CLK 70

ODCK, HSYNC,

VSYNC,DE

CY_OUT,

CB_OUT,

CR_OUT

UPDATE_SW

OCM_UDO_O

OCM_UDI_O

Q11 – Q4,

Q23 – Q16,

Q35 – Q28

V

X

DE

HSYNC

VSYNC

ODCK

X3201

19.6MHz

XTAL

12

TCLK

13

SERIAL FLASH

IC3203

SCK

6

SO

2

SI

5

CE#

1

MSTR_SDATA 29

MSTR_SCLK 28

EEPROM

IC3202

SDA

5

SCL

6

CR_OUT

CY_OUT

CB_OUT

(Page 17)

(Page 17)

(Page 18)

w w w . x i a o y u 1 6 3 . c o m

Q Q 3 7 6 3 1 5 1 5 0

9

9

2

8

9

4

2

9

8

T E L

1 3 9 4 2 2 9 6 5 1 3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com