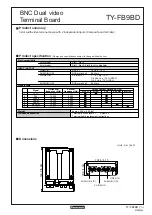

HVR-DR60

4-10

HD-035 (5/5)

XX

R519

XX

C541

XX

C540

NO MARK:REC MODE

0.1

3.2

R0/P3.3

0

0

0

3.2

Note:IC503 can not be replaced,

so that it is not supplied.

DA1

DDQ[24]

0

R501

0

R503

0

R507

0

R510

0

R512

0

R516

0

R524

4700

R520

DD[0]

DDQ[22]

0

R538

R541

0

0.1u

C517

10k

R534

LD[7]

0.1u

C532

DDQ[16]

DD[14]

DDQ[2]

DA[7]

100

R536

DA[1]

10k

R528

INTRQ

DQM0

I2C_SDA

DD[5]

DDQ[7]

#RAS

LCD_RESET

LREQ

DA2

DDQ[14]

LD[3]

DDQ[1]

0.1u

C543

DD[10]

DDQ[0]

DD[1]

DA[8]

DDQ[27]

DA[2]

DMARQ

BA1

G_ALERT

DDQ[3]

#CAS

LCD_CS1

DD[15]

DDQ[26]

LPS

#CS0

DD[6]

#DIOW

0

R517

0

R504

0

R511

DDQ[28]

0

R508

0

R515

0

R523

4700

R522

R540

0

10k

R532

DDQ[31]

LD[4]

DDQ[19]

DA[9]

DD[11]

0.1u

C527

DA[3]

DDQ[9]

33k

R526

SUB_TXD

BA0

MRESET

#WE

DD[2]

DDQ[8]

LKON

#CS1

#DIOR

0.1u

C522

DDQ[5]

A1.8V

LD[0]

DDQ[21]

DD[7]

DDQ[23]

DA[10]

DA[4]

DDQ[18]

SUB_RXD

LD[5]

CLKD

PCLK

220p

C539

DDQ[29]

DQM3

GND

LCD_SDA

DD[12]

DDQ[30]

#RESET

0.1u

C510

#DMACK

0

R502

0

R505

0

R506

M3.3VA

0

R509

DD[3]

0

R514

0

R513

4700

R518

DDQ[17]

4700

R521

0

R539

10k

R529

10k

R537

0.1u

C504

DDQ[6]

LD[1]

DDQ[15]

DA[11]

DA[5]

4700

R525

10k

R531

DD[8]

CLKE

#PDTAG

DDQ[25]

DQM2

0.1u

C546

0.1u

C536

LCD_SCL

CTL1

DDQ[20]

LD[6]

DA0

DDQ[13]

DD[13]

DDQ[4]

DD[4]

DDQ[12]

DA[12]

DA[6]

DA[0]

IORDY

DDQ[10]

DQM1

IND60C32

IC501

B16

AV

2_V

ALI

D

A16

AV

2

_

S

O

P

C16

AV

2

_

S

O

F

B13

AV

2_DA

T

A7

C13

AV

2_DA

T

A6

A14

AV

2_DA

T

A5

B14

AV

2_DA

T

A4

C14

AV

2_DA

T

A3

A15

AV

2_DA

T

A2

B15

AV

2_DA

T

A1

D14

AV

2_DA

T

A0

C15

AV

2_CLK

L19

AV

1_V

ALI

D

L18

AV

1

_

S

O

P

M20

AV

1

_

S

O

F

K20

AV

1_DA

T

A7

K18

AV

1_DA

T

A6

J20

AV

1_DA

T

A5

J19

AV

1_DA

T

A4

J17

AV

1_DA

T

A3

H19

AV

1_DA

T

A2

G20

AV

1_DA

T

A1

F20

AV

1_DA

T

A0

L20

AV

1_CLK

T3

AV

3_CLK

P3

AV

3_DA

T

A0

N3

AV

3_DA

T

A1

N1

AV

3_DA

T

A2

K3

AV

3_DA

T

A3

K2

AV

3_DA

T

A4

J1

AV

3_DA

T

A5

J2

AV

3_DA

T

A6

J4

AV

3_DA

T

A7

U1

AV

3

_

S

O

F

T4

AV

3

_

S

O

P

U2

AV

3_V

ALI

D

Y17

DD14

W17

DD13

V20

DD12

T18

DD11

T20

DD10

P20

DD9

N19

DD8

M18

DD7

N18

DD6

P19

DD5

T19

DD4

U20

DD3

T17

DD2

V16

DD1

W16

DD0

V14

DIOW

-

Y15

DIOR-

W11

DMACK-

W9

DA0

Y10

DA1

V9

DA2

U9

CS0-

Y8

CS1-

V10

RESET-

W15

DMAREQ

Y11

INTRQ

W14

IORDY

M19

PDIAG-

Y18

ATAEN

C12

LCLK

B6

CTL1

A5

CTL0

D7

LREQ

A12

LPS

C6

PCLK

D12

PINT

B12

LINKON

V3

RST-

G1

GPIO7

C2

GPIO6

B1

GPIO5

F3

GPIO4

E1

GPIO3

E3

GPIO2

C1

GPIO1

D3

GPIO0

Y4

SCL

Y5

SDA

C18

UART_TX

A20

UART_RX

W20

XPRINT

V19

XPCS-

W18

XPRD-

V17

XPWR-

V18

XPA2

W19

XPA1

Y20

XPA0

M1

PLL1FILTER

M2

PLL2FILTER

A9

PLL3FILTER

L1

CLK

V5

XPD0

W5

XPD1

W6

XPD2

Y6

XPD3

V7

XPD4

W7

XPD5

Y7

XPD6

V8

XPD7

W8

XPO8

V12

XPD9

U12

XPD10

Y13

XPD11

W13

XPD12

V13

XPD13

Y14

XPD14

U16

XPD15

C19

SRESET-

E17

SCS-

D19

SWE-

D20

SD

F18

SI

E20

SCLK

A2

TRST

B2

TDO

B3

TDI

C4

TMS

B5

TCK

U19

DQ31

U18

DQ30

R19

DQ29

R20

DQ28

B11

LD7

V15

DD15

U5

AV

4_V

ALI

D

C7

LD0

V4

AV

4

_

S

O

P

A6

LD1

W4

AV

4

_

S

O

F

B7

LD2

Y3

AV

4_DA

T

A

A7

LD3

W3

AV

4_CLK

A10

LD4

R3

AV

3_DREQ

A11

LD5

H2

AV

3_IRC

C11

LD6

K19

DQ27

J18

DQ26

H20

DQ25

H18

DQ24

G19

DQ23

G18

DQ22

G17

DQ21

E19

DQ20

E18

DQ19

C20

DQ18

D18

DQ17

B20

DQ16

B19

DQ15

A19

DQ14

B17

DQ13

C17

DQ12

D16

DQ11

A18

DQ10

C10

DQ9

D9

DQ8

A8

DQ7

B8

DQ6

C8

DQ5

A4

DQ4

C5

DQ3

B4

DQ2

A3

DQ1

D5

DQ0

C9

CLKD

A17

CKE

W2

A0

W1

A1

V2

A2

U3

A3

P4

A4

R2

A5

R1

A6

P2

A7

N2

A8

M4

A9

K1

A10

J3

A11

T2

A12

E4

BA0

D2

BA1

H1

DQM0

H3

DQM1

G3

DQM2

F1

DQM3

G4

WE-

F2

CAS-

E2

RAS-

D1

CS-

U11

VSSA

L3

VSS_PLL1

M3

VSS_PLL2

B9

VSS_PLL3

W10

VSS1

U14

VSS2

P17

VSS3

M17

VSS4

A1

VSS5

D4

VSS6

D8

VSS7

D13

VSS8

D17

VSS9

H4

VSS10

H17

VSS11

J9

VSS12

J10

VSS13

J11

VSS14

J12

VSS15

K9

VSS16

K10

VSS17

K11

VSS18

K12

VSS19

L9

VSS20

L10

VSS21

L11

VSS22

L12

VSS23

M9

VSS24

M10

VSS25

M11

VSS26

M12

VSS27

N4

VSS28

N17

VSS29

U4

VSS30

U8

VSS31

U13

VSS32

U17

VSS33

D6

VDD181

D11

VDD182

D15

VDD183

F4

VDD184

F17

VDD185

K4

VDD186

L17

VDD187

R4

VDD188

R17

VDD189

U6

VDD1810

U10

VDD1811

U15

VDD1812

Y9

VDD331

Y1

VDD332

Y16

VDD333

R18

VDD334

N20

VDD335

G2

VDD336

P1

VDD337

V1

VDD338

Y2

VDD339

U7

VDD3310

W12

VDD3311

Y19

VDD3312

P18

VDD3313

K17

VDD3314

F19

VDD3315

B18

VDD3316

A13

VDD3317

B10

VDD3318

C3

VDD3319

T1

VDD3320

V6

VDD3321

L2

VDD18_PLL1

L4

VDD18_PLL2

D10

VDD18_PLL3

Y12

VDD18A

V11

VDD33A

I2C_SCL

LD[2]

DDQ[11]

#CS

LCD_A0

0.1u

C545

CTL0

DD[9]

CL513

CL501

CL511

CL502

CL516

CL514

CL512

CL515

CL509

CL510

CL505

CL508

CL507

CL506

CL503

CL504

CL522

CL523

CL518

CL521

CL517

CL520

CL519

0.1u

C549

0.1u

C551

0.1u

C552

0.1u

C553

0.1u

C554

0.1u

C555

0.1u

C556

0.1u

C557

0.1u

C558

0.1u

C559

0.1u

C560

CL526

CL529

CL527

CL524

CL528

CL525

CL530

CL532

CL531

CL538

CL534

CL535

CL536

CL533

CL537

CL539

CL541

CL540

CL542

CL543

JL502

JL507

JL506

JL503

JL505

JL501

JL504

JL513

JL516

JL515

JL518

JL511

JL514

JL512

JL517

R542

0

R543

0

R544

0

0

R545

0

R546

0

R547

0

R548

0

R549

0

R550

FB504

1k

R551

C561

0.01u

FB501

FB502

1.8V

M3.3V

10u

C562

10u

C563

33

R553

33

R554

C564

0.1u

SUB_S_RESET

SUB_S_CNVSS

C538

4.7u

4.7u

C548

4.7u

C550

0.01u

C537

AT45DB081B-CNU

IC503

1

SI

2

SCK

3

RESET

4

CS

5

WP

6

Vcc

7

GND

8

SO

FB505

0uH

FB506

0.001u

C565

0.001u

C566

0

R552

S3.3V

X503

27MHz

1

4

3

2

1

A

M3.3VMAIN

DDQ[28]

DDQ[27]

DDQ[25]

DDQ[24]

DDQ[23]

DDQ[22]

DDQ[21]

DDQ[20]

DDQ[19]

DDQ[18]

DDQ[17]

DDQ[16]

DDQ[15]

DDQ[14]

DDQ[13]

DDQ[12]

DDQ[11]

DDQ[10]

DDQ[9]

DDQ[8]

DDQ[7]

DDQ[6]

DDQ[5]

DDQ[4]

DDQ[3]

DDQ[2]

DDQ[31]

DDQ[1]

DDQ[30]

DDQ[0]

DDQ[29]

LCD_CS1

LCD_RESET

LCD_A0

LCD_SCL

LCD_SDA

G_ALERT

LCD_CS1

LCD_RESET

LCD_A0

LCD_SCL

LCD_SDA

G_ALERT

LD[0]

LD[1]

LD[2]

LD[3]

LD[4]

LD[5]

LD[6]

LD[7]

LD[0]

LD[1]

LD[2]

LD[3]

LD[4]

LD[5]

LD[6]

LD[7]

DD[0]

DD[1]

DD[2]

DD[3]

DD[4]

DD[5]

DD[6]

DD[7]

DD[8]

DD[9]

DD[10]

DD[11]

DD[12]

DD[13]

DD[14]

DD[15]

DD[0]

DD[1]

DD[2]

DD[3]

DD[4]

DD[5]

DD[6]

DD[7]

DD[8]

DD[9]

DD[10]

DD[11]

DD[12]

DD[13]

DD[14]

DD[15]

BA0

BA1

DQM0

DQM1

DQM2

DQM3

#WE

#CAS

#RAS

#CS

BA0

BA1

DQM0

DQM1

DQM2

DQM3

#WE

#CAS

#RAS

#CS

DA[0]

DA[1]

DA[2]

DA[3]

DA[4]

DA[5]

DA[6]

DA[7]

DA[8]

DA[9]

DA[10]

DA[11]

DA[12]

DA[0]

DA[1]

DA[2]

DA[3]

DA[4]

DA[5]

DA[6]

DA[7]

DA[8]

DA[9]

DA[10]

DA[11]

DA[12]

CLKD

CLKE

CLKD

CLKE

DDQ[26]

DDQ[0]

DDQ[1]

DDQ[2]

DDQ[3]

DDQ[4]

DDQ[5]

DDQ[6]

DDQ[7]

DDQ[8]

DDQ[9]

DDQ[11]

DDQ[12]

DDQ[13]

DDQ[14]

DDQ[15]

DDQ[16]

DDQ[17]

DDQ[18]

DDQ[19]

DDQ[20]

DDQ[21]

DDQ[22]

DDQ[23]

DDQ[24]

DDQ[25]

DDQ[26]

DDQ[27]

DDQ[28]

DDQ[29]

DDQ[30]

DDQ[31]

DDQ[10]

TMS

TCK

TDI

TDO

TRST

VCC

GND

CNVSS

VCC

TXD

BUSY

VSS

RXD

SCLK

RESET

B

H

G

L

C

K

E

I

D

HD-035 BOARD(5/5)

F

J

08

IC501

DV SIGNAL PROCESS

IC503

FLASH MEMORY

(4/5)

(2/5)

@004

M

(3/5)

@006

@008

(4/5)

@007

(4/5)

(3/5)

(1/5)

(1/5)

(1/5)

(4/5)

(2/5)

@002

(1/5)

DV SIGNAL PROCESS

XX MARK:NO MOUNT

8

18

5

12

9

2

13

10

4

14

11

16

7

15

6

17

3

1.8V

A1.8V

M3.3VA

:Voltage measurement of the CSP ICs

and the Transistors with mark,are

not possible.