– 33 –

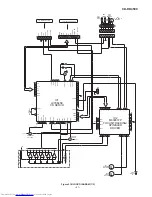

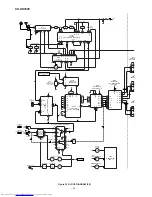

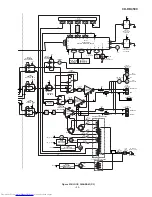

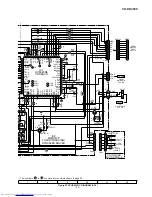

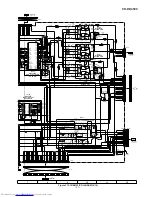

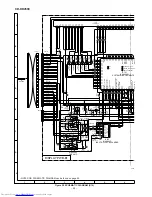

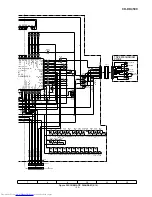

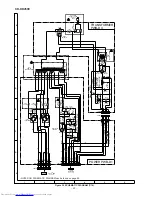

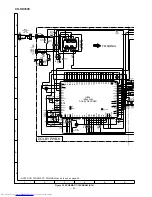

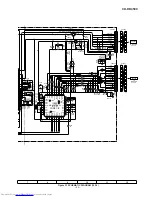

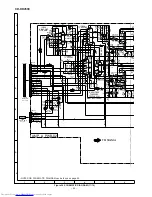

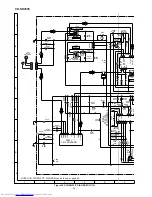

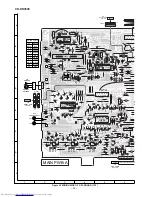

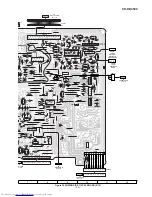

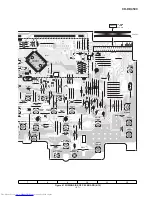

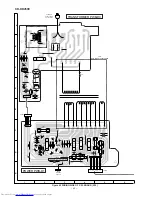

CD-DD4500

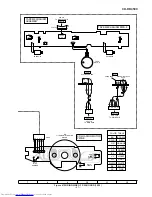

Figure 33 SCHEMATIC DIAGRAM (10/14)

7

8

9

10

11

12

44

43

42

41

40

39

38

37

36

35

34

34

22

20

19

18

17

16

15

14

13

12

1 2 3 4 5 6

8

7

9

10 11

33 32 31 30 29 28 27 26 25 24 23

PDN

LOOP0

DIF1

DIF0

P/S

MCLK

DZF1

AVSS

AVDD

VREFH

VCOM

DZF2

RIN–

RIN+

LIN+

LIN–

ROUT3

LOUT1

LOUT2

LOUT3

22

21

CAD0

CAD1

ADIF

NC

TST

DVSS

DVDD

TVDD

DZFE

NC

DFS

DAUX

SDTO

SDTI3

SDTI2

SDTI1

LRCK

BICK

SMUTE

I2C

SDOS

44

21

LOOP1

ROUT2

ROUT1

RF

AGND

LF

AGND

SW

AGND

CENTER

AGND

RS

AGND

LS

AGND

RO

AGND

LO

2

3

4

5

6

7

8

9

10

11

12

13

14

15

1

FFC607

TO

MAIN PWB

P27 7-A

STATUS

LOCK

RESET

DDLAT

DDAC

DIO

CK

DDCE

A10V

D5V

DGND

2

3

4

5

6

7

8

9

10

11

12

1

2

1

1

2

1

3

BI501A

BI501B

2

CNP607

FFC602

TO

MAIN PWB

P26 5-A

CNP602

12

1

15

1

1

12

1

15

+B

+B

+B

+B

+B

+B

+B

+B

+B

+B

+B

+B

+B

B

+B

+B

C523 0.01

C524

0.47

R513

100

C578 0.022

C579 0.022

C7015 0.022

D512

1SS133

D513

1SS133

C7016 0.022

D502

1SS133

D503

1SS133

CX04 0.022

D510 1SS133

D511

1SS133

C538

0.001

C577 0.022

Q520

KRC104 M

L570

0.82

µ

H

R574

4.7K

C554

0.1

C552

10/16

R538

4.7K

Q572

2SD468-C

C576

0.022

R578 390

R577 390

C574 47/25

DZ571

MTZJ5.6A

C575

100/10

C573

100/10

C571

47/16

IC571

TA48M033F(S)

3.3 V VOLTAGE REGULATOR

2

1

C555 0.1

R573 4.7K

R537 4.7K

C553

10/16

CNP503

CNP502

C526 10/16

C525

0.1

R512

15K

C527 100P (CH)

R514

10K

R510

1K(F)

C528 120P(CH)

R509 1K(F)

R511 10K

9

R515

4.7K

C540 10/16

C541 10/16

C542 10/16

C543 10/16

C544 10/16

C556 0.001

C531

0.1

R556

470

C533

0.1

IC505

AK4527BVQ

6-CH

CODEC IC

R559 470

C530

10/16

C545 10/16

C557

0.001

R557 470

R558 470

C532

2.2/50

C535

0.01

C536

0.1

C537

10/16

R540

10K

R541

10K

R531

1K

R530

1K

R549 27K

R550 27K

R551 27K

R552 27K

R553 27K

R554 27K

R536

100K

R535

100K

C546 0.015

C547 0.015

C548 0.015

C549 0.015

C550 0.015

C551

0.015

C558 4.7/25

C559 4.7/25

R544 220

R545 220

R546 220

R547 220

R548 220

R543 220

R542

10K

3

R532

10K

Содержание CD-DD4500

Страница 70: ...CD DD4500 70 MEMO ...

Страница 87: ...CD DD4500 16 MEMO ...