GSM/GPRS/GNSS Module Series

MC60 Series Hardware Design

MC60_Series_Hardware_Design Confidential / Released 54 / 114

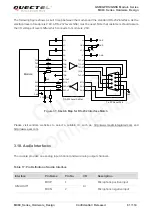

The logic levels are described in the following table.

Table 15: Logic Levels of the UART Interface

Table 16: Pin Definition of the UART Interfaces

Parameter

Min.

Max.

Unit

V

IL

0

0.25 × VDD_EXT

V

V

IH

0.75 × VDD_EXT

0.2

V

V

OL

0

0.15 × VDD_EXT

V

V

OH

0.85 × VDD_EXT

VDD_EXT

V

Interface

Pin Name

Pin No.

I/O

Description

UART Port

TXD

33

DO

Transmit data

RXD

34

DI

Receive data

DTR

37

DI

Data terminal ready

RI

35

DO

Ring indication

DCD

36

DO

Data carrier detection

CTS

38

DO

Clear to send

RTS

39

DI

Request to send

Debug Port

DBG_RXD

30

DI

Receive data

DBG_TXD

29

DO

Transmit data

Auxiliary UART Port

1)

RXD_AUX

1)

24

DI

Receive data

TXD_AUX

1)

25

DO

Transmit data

GNSS UART Port

GNSS_RXD

23

DI

Receive data

GNSS_TXD

22

DO

Transmit data

Quectel

Confidential