TH-65PF11EK

43

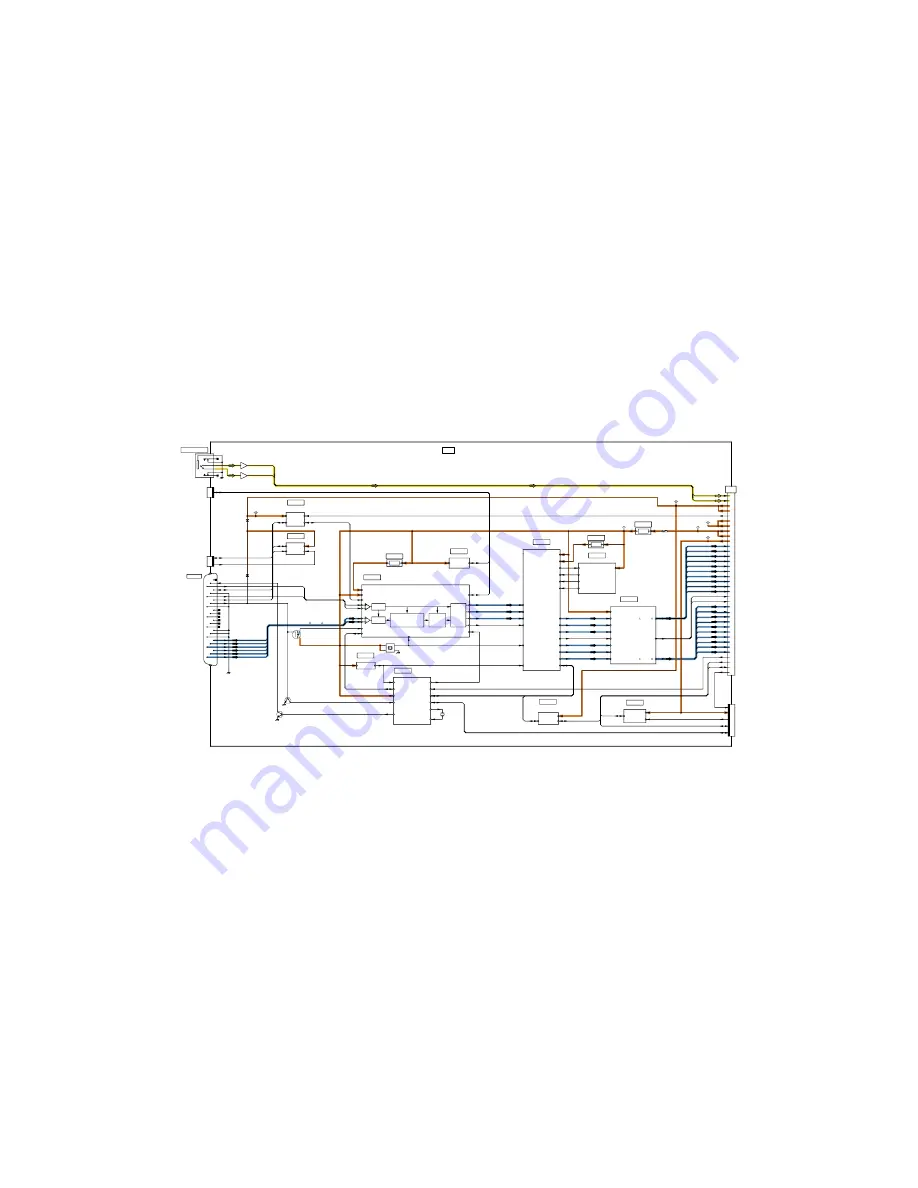

10.3. Block (3 of 9) Diagram

T

TMDS_RX0-

T

TMDS_RX1-

TMDS_RX2-

T

T

TMDS_RXC-

DVI_CN_SDA

DVI_CN_SCL

AUDIO_L

AUDIO_R

AUDIO_R

AUDIO_L

JK3301

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

JK3302

D3011

Q3304

+5V

D3025

Q3301

Q3305

X3301

1

OE

2

GND

3

OUT

4

VDD

X3302

+3.3V

PA3301

+15V

+5V

N.C.

N.C.

TMDS_G

TMDS_G

TMDS_G

TMDS_D2-

TMDS_D1-

TMDS_D0-

N.C.

N.C.

DVI IN

+5V

GND

DDCD

N.C.

TMDS_G

HPS

DDCC

N.C.

TMDS_C-

H4

FOR

FACTORY

USED

R

L

DVI AUDIO IN

FOR

FACTORY

USED

H2

IC3301

EEPROM

SDA

SCL

WC

VCC

EDID_WP

DVI_CN_SDA/SCL

B

OE2

LEVEL SHIFT

A

IC3303

VCC

5V<->3.3V

SDA/SCL

DVI_5V_DET

PLL

LATCH

SYNCHRONIZATION

DATA RECOVERY

AND

TMDS

DECODER

RGB

OUTPUT

R0-R7

G0-G7

B0-B7

HSYNC,VSYNC,DOCK

R1PWR5V

CSDA/CSCL

VCC(+3.3V)

DSCL1/DSA1

VCC(+1.8V)

RESET

XTAL IN

EPCS_DATA

EPCS_ASD

EPCD_DCLK

DVI I/F RECEIVER

IC3307

SDA0

SCL0

HPD

DVI_5V_DET

VCC(+3.3V)

IC3312

VCC

RESET

VOUT

GENX MPU

IC3310

NRST

RESET

N_FHD

SDA2

SCL2

SDA1

SCL1

10MHz

OSCXO

OSCXI

+1.8V

IC3308

H,V,CK

R0-R7

B0-B7

G0-G7

CLK7(27MHz)

NRST

DATA

ASD

DCLK

CONFIG ROM

VCC

IC3314

DVI_IIC

TMDS RX0

-RX2

+1.2V

IC3342

GENX_COMTROL_IIC

TVLOAD_IIC

IC3320

SLOT_IIC

VCC

B

IC3319

VCC

WR

EEPROM

SDA/

SCL

A

LEVEL SHIFT

5V<->3.3V

H3

FOR

FACTORY

USED

SLOT_IIC

VCC(+1.2V)

VCC(+3.3V)

O_CLK

CLK4

S2

S1

FREQ0

FREQ1

XIN

CKOUT

VCC(+3.3V)

IC3343

CPG

IC3341

FPGA

Q3302

Q3303

B0-B7

G0-G7

EVEN_R0-R7

EVEN_G0-G7

EVEN_B0-B7

H,V,CLK

H,V,CK

R0-R7

ODD_B0-B7

ODD_G0-G7

B0-B7

R0-R7

G0-G7

ODD_R0-R7

VCC(+3.3V)

SDA/SCL

IC3346

LVDS TX

B14

B12

L

B2

L

L

H1

LVDS_TX3-

LVDS_TX0-

LVDS_TX1-

LVDS_TX4-

L

L

B15

A2

LVDS_TX2-

L

LVDS_TXC-

B11

B8

B9

TO SLOT2

B5

A3

B3

SRQ

IIC_SCL

IIC_SDA

B24

B25

HD/FHD DET

A23

+3.3V

IC3345

PLUG DET

B39

TA1

-TE1

TCK1

TA2

-TE2

A19

+5V

+5V

B19

+9V

+9V

+9V

B21

STB+5V

A22

STB+5V

+15V

B38

+15V

A28

A26

AUDIO_OUT_R

AUDIO_OUT_L

A7

LVDS_TX6-

L

A15

L

L

A14

LVDS_TX5-

A4

A13

LVDS_TX8-

L

A10

LVDS_TX7-

A12

L

LVDS_TX9-

A9

TA1+

TA1-

TE2+

TE2-

TC2-

TC2+

TE1-

TE1+

TB1-

TB1+

TD1-

TD1+

TA2-

TD2+

TB2-

TB2+

TD2-

TC1-

TC1+

TA2+

TCK1-

TCK1+

A21

B37

A5

B6

A8

B23

TH-65PF11EK

Block (3 of 9) Diagram

TH-65PF11EK

Block (3 of 9) Diagram

DVI INTERFACE

HDE

Содержание TH-65PF11EK

Страница 7: ...7 TH 65PF11EK 3 2 Applicable signals ...

Страница 9: ...9 TH 65PF11EK 5 Operating Instructions ...

Страница 14: ...14 TH 65PF11EK 6 2 IIC mode structure following items value is sample data ...

Страница 35: ...35 TH 65PF11EK 9 1 4 Adjustment Volume Location 9 1 5 Test Point Location ...

Страница 37: ...37 TH 65PF11EK ...

Страница 39: ...39 TH 65PF11EK ...

Страница 40: ...40 TH 65PF11EK ...

Страница 50: ...TH 65PF11EK 50 ...

Страница 51: ...51 TH 65PF11EK 11 Wiring Connection Diagram 11 1 Wiring 1 ...

Страница 52: ...52 TH 65PF11EK 11 2 Wiring 2 ...

Страница 53: ...53 TH 65PF11EK 11 3 Wiring 3 ...

Страница 54: ...54 TH 65PF11EK ...

Страница 55: ...TH 65PF11EK 55 12 Schematic Diagram 12 1 Schematic Diagram Notes ...

Страница 185: ...Model No TH 65PF11EK Note ...

Страница 186: ...Model No TH 65PF11EK Exploded View ...

Страница 187: ...Model No TH 65PF11EK Cabinet part location ...

Страница 188: ...Model No TH 65PF11EK Fan part location ...

Страница 189: ...Model No TH 65PF11EK Flat cable ...

Страница 190: ...Model No TH 65PF11EK Accessories ...

Страница 191: ...Model No TH 65PF11EK Packing 1 ...

Страница 192: ...Model No TH 65PF11EK Packing 2 ...