Pin

No.

Mark

I/O

Function

1

DACRST

O

DAC reset signal output terminal to

IC4 (“L”:Reset)

2

DEO

O

DE emphasis signal output terminal

to IC4(“L”:DE emphases)

3

MUTE

—

AD-DA mute output terminal (Not

used, open)

4

AD RST

O

Reset signal output terminal

5

NRFSTBY

O

Standby control signal output

terminal (“L”:Standby)

6

PC

O

Transistor drive signal output

terminal (“H”:Power ON)

7

MSP RST

O

MSP reset signal output terminal

(“L”:Reset)

8

LOAD1

O

Loading motor drive 1 output

terminal

9

LOAD0

O

Loading motor drive 0 output

terminal

10

NEFMON

O

Magnetic head current output

terminal

11

TEST01

O

Test signal output terminal (Not

used, open)

12

TVSW

I

Traverse innermost detection switch

signal input terminal

13

DISC IN

I

Disc detection switch signal input

terminal

14

REFLECT

I

Reflection rate switch signal input

terminal

15

LOAD SW0

(OPEN)

I

Loading

mechanism

position

det.

Switch 0 signal input terminal

16

LOAD SW1

(TRG)

I

Loading mechanism position det.

Switch 1 signal input terminal

17

LOAD SW2

(PLAY/REC)

I

Loading mechanism position det.

Switch 2 signal input terminal.

18

LOAD SW3

(PLAY)

I

Loading mechanism position det.

Switch 3 signal input terminal

19

PROTECT

I

Erase prevention switch signal input

terminal

20

MMOD

—

Connected to GND

21

RST

I

Reset signal input terminal

(“L”:Reset)

22

UNIT TEST

I

Test signal input terminal (Open)

23

CS2

I

Test signal input terminal (Open)

24

SCTSY

I

Micro computer interrupt signal input

terminal (SUBQ/ADIP simultaneous

signal)

25

MDISY

I

Micro computer interrupt signal input

terminal (MD simultaneous signal)

26

PANEL

REQ

I

Panel I/F request signal input

terminal

27

~29

LED OUT1

~LED OUT3

O

Drive signal output terminal to LED

DRIVE (“H”:LED ON)

30

TEST02

O

Test signal output terminal (Not

used, open)

31

V

DD

2(3V)

I

Power supply terminal (+3V)

32

OSC1

I

Crystal oscillator input terminal

(f=10.02MHz)

33

OSC2

O

Crystal oscillator output terminal

(f=10.02MHz)

34

V

SS

—

GND terminal

35

X1

I

Not used, connected to GND

36

X0

O

Not used, open

37

VSS

—

GND terminal

38

TEST03

O

Test signal output terminal (Not

used, open)

39

EEPCS

O

EEPROM chip select signal output

terminal (Not used, open)

40

EEPCK

O

EEPROM clock signal output

terminal (Not used, open)

Pin

No.

Mark

I/O

Function

41

EEPDATA

I/O

EEPROM data in/output terminal

(Connected to GND through resistor)

42

TEST04

O

Test signal output terminal (Not

used, open)

43

TEST05

44

CFSYNC

I

ATRACK management frame

simultaneous signal input terminal

45

TEST06

O

Test signal output terminal (Not

used, open)

46

TEST07

I

Connected to rec/play switch signal

47

TOK OK

O

Not used, open

48

HF ON

—

Drive signal output terminal to Q3

(POWER SUPPLY CONTROL)

49

PANEL CLK

I

Panel I/F clock input terminal

50

PANEL

DATA I

I

Panel I/F data input terminal

51

PANEL

DATA 0

O

Panel I/F data output terminal

52

PANEL CS

O

Panel I/F chip select output terminal

53

SELAD

O

Micro computer I/F address select

output terminal

54

SSCLK

O

Micro computer I/F clock output

terminal

55

SSDR

I

Micro computer I/F reading data

input terminal

56

SSDW

O

Micro computer I/F writing data

output terminal

57

LCDCK

O

LCD clock test signal output terminal

(Connected to power supply through

resistor)

58

ADRS

TEST RXD

O

Test signal output terminal

(Connected to power supply through

resistor)

59

LCD DATA

TXD

O

Test signal output terminal (Not

used, open)

60

VREF-

—

Connected to GND

61

TEMP

I

Temprature sensor amp input

terminal

62

KEY1

I

Key input 1 terminal

63

KEY2

I

Key input 2 terminal

64

MO LOAD

I

Test signal input terminal

(“L”:Without loading mechanism)

(Open)

65

SRVTEST

I

Test signal input terminal (“L”:Servo

test mode) (Open)

66

LOAD P

I

Test signal input terminal (Open)

67

TEST KEY

IN

I

Test signal input terminal (“L”:Unit

key mode) (Open)

68

SRV LOAD

I

Test signal input terminal (“L”:Using

for servo primary values EEPROM)

69

VCC 3V

I

Power supply terminal (+3V)

70

VCC 5V

I

Power supply terminal (+5V)

71

SELADDA

I

AD/DA converter select signal input

terminal (Open)

72

SLOCK

O

Spindle lock test signal output

terminal (Not used, open)

73

TLOCK

O

Tracking lock signal output terminal

(“H”:lock) (Not used, open)

74

FLOCK

O

Focus lock test signal output

terminal (“H”:lock) (Not used, open)

75

ERROR

O

Servo error test signal output

terminal (Not used, open)

76

BUSY

O

Servo busy test signal output

terminal (Not used, open)

77

SBPRETRY

O

Signal management retry test signal

output terminal (Not used, open)

78

SRVRETRY

O

Servo retry test signal output

terminal (Not used, open)

79

ARDSKIP

O

Address skip test signal output

terminal (Not used, open)

12.4. IC10 (MNBDF03DAA1) : SYSTEM CONTROL

28

SA-PM30MD

Содержание SA-PM30MD

Страница 6: ...6 Caution for AC Mains Lead 6 SA PM30MD ...

Страница 7: ...7 Operation Procedures 7 SA PM30MD ...

Страница 8: ...8 SA PM30MD ...

Страница 74: ...16 Wiring Connection Diagram 74 SA PM30MD ...

Страница 75: ...17 Troubleshooting Guide 75 SA PM30MD ...

Страница 76: ...76 SA PM30MD ...

Страница 77: ...77 SA PM30MD ...

Страница 78: ...78 SA PM30MD ...

Страница 79: ...79 SA PM30MD ...

Страница 80: ...80 SA PM30MD ...

Страница 81: ...81 SA PM30MD ...

Страница 82: ...82 SA PM30MD ...

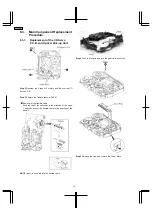

Страница 84: ...18 1 1 Deck Mechanism Parts Location 18 1 Deck Mechanism RAA4106 84 SA PM30MD ...

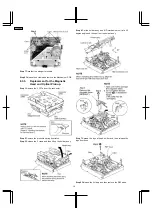

Страница 86: ...18 2 MD Mechanism 18 2 1 MD Mechanism Parts location 86 SA PM30MD ...

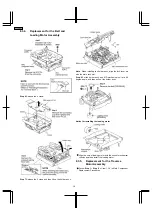

Страница 88: ...18 3 CD Loading Mechanism 18 3 1 CD Loading Mechanism Parts Location 88 SA PM30MD ...

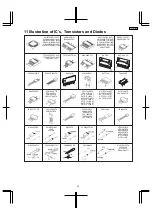

Страница 90: ...18 4 1 Cabinet Parts Location 18 4 Cabinet 90 SA PM30MD ...

Страница 91: ...91 SA PM30MD ...