DV-CP802

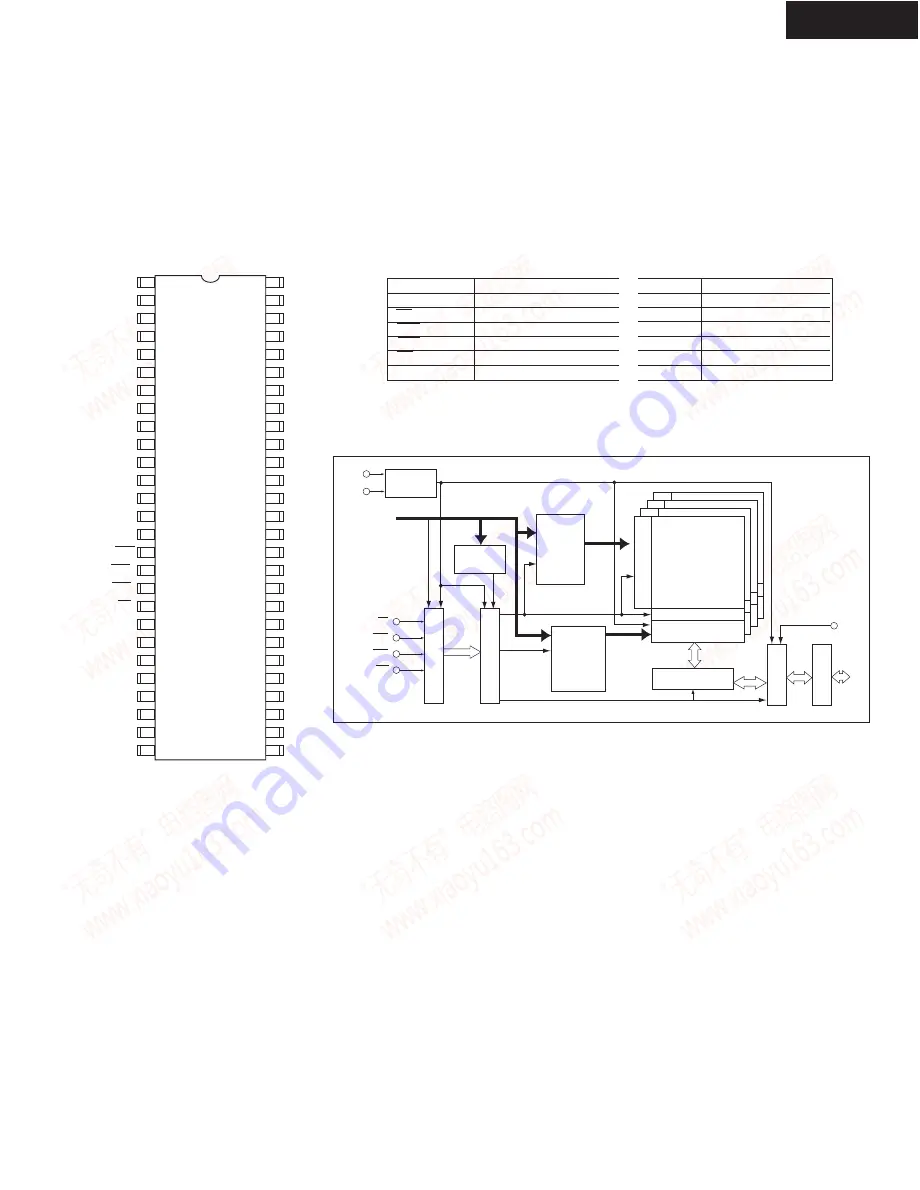

IC BLOCK DIAGRAM AND TERMINAL DESCRIPTIONS-27

Q2303 : IC42S16400-7T SYNCHRONOUS DYNAMIC RAM

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

V

SS

DQ15

V

SSQ

DQ14

DQ13

V

DDQ

DQ12

DQ11

V

SSQ

DQ10

DQ9

V

DDQ

DQ8

V

SS

NC

UDQM

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

V

SS

V

DD

DQ0

V

DDQ

DQ1

DQ2

V

SSQ

DQ3

DQ4

V

DDQ

DQ5

DQ6

V

SSQ

DQ7

VDD

LDQM

WE

CAS

RAS

CS

BA0

BA1

A10

A0

A1

A2

A3

V

DD

Row

Address

Buffer

and

Refresh

Counter

Column

Address

Buffer

and

Burst

Counter

Mode

Register

Clock

Generator

Control Logic

Command Decoder

CS

RAS

CAS

WE

Data Control Circuit

Sense Amplifier

Column Decoder &

Latch Circuit

Row Decoder

Bank D

Bank C

Bank B

Bank A

Latch Circuit

Input & Output

Buffer

DQM

DQ

CLK

CKE

Address

Master Clock

Clock Enable

Chip Select

Row Address Strobe

Column Address Strobe

Write Enable

Data I/O

DQM

A0 - 11

BA0, 1

V

DD

V

DDQ

V

SS

V

SSQ

CLK

CKE

CS

RAS

CAS

WE

DQ0 - DQ15

DQ Mask Enable

Address Input

Bank Address

Power Supply

Power Supply for DQ

Ground

Ground for DQ

The IC42S16400 are high-speed 67, 108, 864-bit synchronous dynamic ramdam-access

memories, organized as 2,097, 152 x 8 x 4 and 1,48, 576 x 16 x 4 (word x bit x bank), respectively.

The synchronous DRAMs achieved high-speed data transfer using the pipeline architecture and clock

frequency up to 133MHz for -7.

All input and outputs are synchronized with the positive edge of the clock. The synchronous DRAMs are

compatible with Low Voltage TTL.

PIN CONFIGURATIONS

PIN DESCRIPTIONS

BLOCK DIAGRAM

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299