338

µ

PD78214 Sub-Series

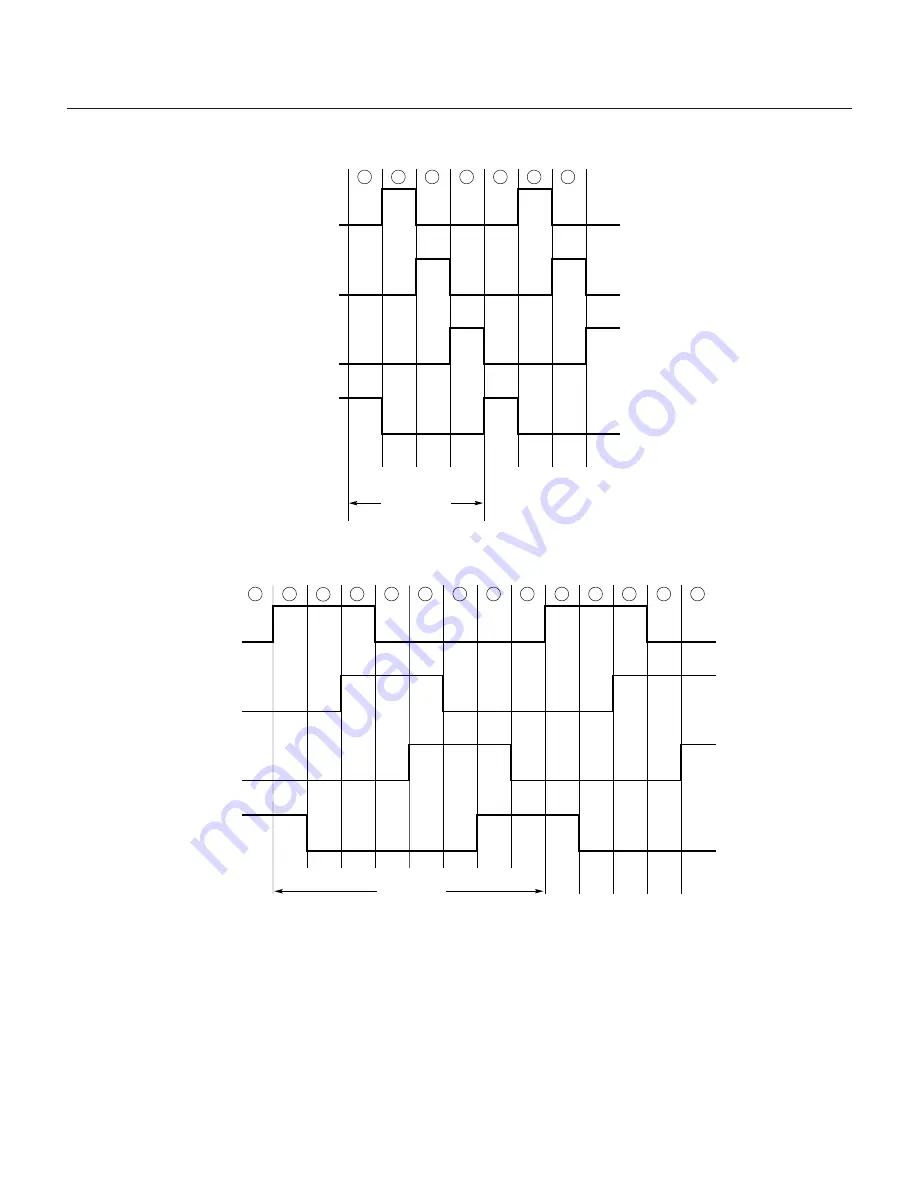

Fig. 12-29 Four-Phase Stepping Motor with Phase 1 Excitation

Fig. 12-30 Four-Phase Stepping Motor with Phases 1 and 2 Excitation

1

2

3

4

1

2

3

1 cycle

(4 patterns)

Phase A

Phase B

Phase C

Phase D

1

8

2

3

4

5

6

7

8

1

2

3

4

5

1 cycle

(8 patterns)

Phase A

Phase B

Phase C

Phase D

Содержание PD78212

Страница 11: ......

Страница 53: ...24 ...

Страница 61: ...32 µPD78214 Sub Series 9 VSS Ground 10 NC non connection Not connected inside the chip ...

Страница 65: ...36 ...

Страница 83: ...54 ...

Страница 135: ...106 ...

Страница 271: ...242 ...

Страница 405: ...376 ...

Страница 417: ...388 ...

Страница 423: ...394 ...

Страница 449: ...420 ...

Страница 457: ...428 ...

Страница 471: ...442 ...

Страница 487: ...458 ...