MOTOROLA

SEMICONDUCTOR PRODUCT INFORMATION

DSP56362

Order this document by:

DSP56362P/D

REV. 2

©1999 MOTOROLA, INC.

DSP56362 Product Brief

Product Brief

This document contains information on a new product. Specifications and information herein are subject to change without notice.

24-BIT AUDIO DIGITAL SIGNAL PROCESSOR

The DSP56362 is a high performance DSP optimized for cost-sensative consumer audio

applications. A general purpose DSP56362 is available as well as a multimode, multichannel audio

decoder for consumer applications such as Audio/Video (A/V) receivers, surround sound decoders,

Digital Versatile Disk (DVD) players, digital TV, and other audio applications. The DSP56362

supports all of the popular multichannel audio decoding formats, including Dolby Digital Surround,

Moving Picture Experts Group Standard 2 (MPEG2), and Digital Theater Systems (DTS), in a single

device with sufficient MIPS resources for customer defined post-processing features such as bass

management, 3D virtual surround, Lucasfilm THX5.1, soundfield processing, and advanced

equalization.

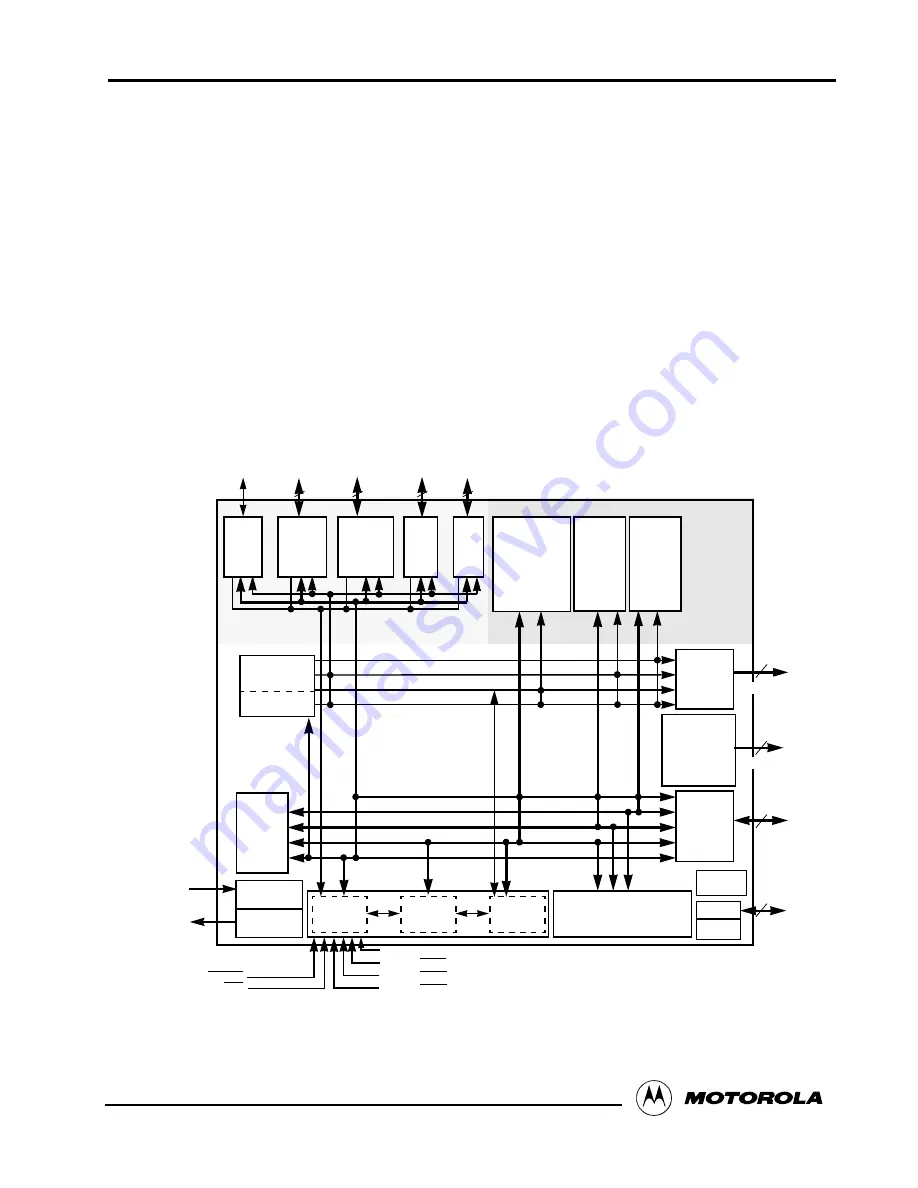

The DSP56362, Figure 1,is member of the 56300 Motorola Symphony™ DSP Family. The

DSP56362 utilizes the single-instruction-per-clock-cycle DSP56300 core, while retaining code

compatibility with the DSP56000 core family. The DSP56362 contains audio-specific peripherals and

an on-board software architecture as shown in Figure 2 and is offered in a 100/120 MHz/MIPS

version at a nominal 3.3 V.

Figure 1 DSP56362 Block Diagram

PLL

OnCE

™

Clock

Generator

Internal

Data

Bus

Switch

YAB

XAB

PAB

YDB

XDB

PDB

GDB

MODB/IRQB

MODC/IRQC

External

Data Bus

Switch

11

MODD/IRQD

DSP56300

12

16

24-BIT

24

18

DDB

DAB

Peripheral

Core

YM

_

EB

XM

_

E

B

PM

_

EB

PI

O

_

EB

Expansion Area

SHI

JTAG

6

5

RESET

MODA/IRQA

PINIT/NMI

EXTAL

Address

Control

Data

Triple

Timer

Host

Interface

ESAI

Address

Generation

Unit

Six Channel

DMA Unit

Program

Interrupt

Controller

Program

Decode

Controller

Program

Address

Generator

Data ALU

24

×

24 + 56

→

56-bit MAC

Two 56-bit Accumulators

56-bit Barrel Shifter

Power

Mgmt.

DRAM/SRAM

Bus

Interface

&

I - Cache

Control

External

Address

Bus

Switch

AA0456G

Memory

Expansion

Area

Program RAM/

Instruction

Cache

3072

×

24

Program ROM

30K

×

24

Bootstrap ROM

X Data

RAM

5632

×

24

ROM

6144

×

24

Y Data

RAM

5632

×

24

ROM

6144

×

24

CLKOUT

DAX

(SPDIF)

2

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..