VSC8502 Reference Board

VPPD-03822 VSC8502 User Guide Revision 1.0

6

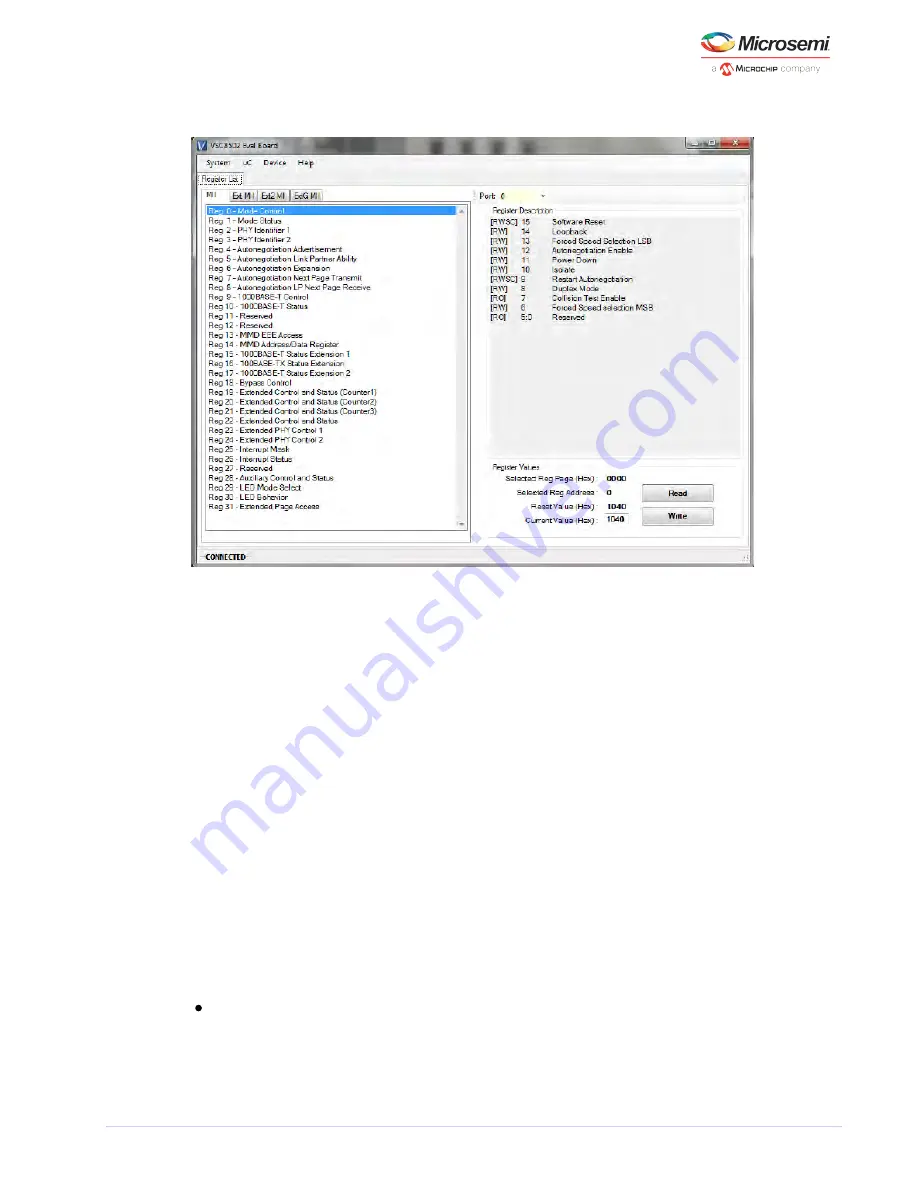

Figure 4 • MII Registers GUI Window

Verify the device is up and running by reading MII Register 0. It should read back 0x1040. Reading back

all 0’s or all 1’s indicates a problem. For a multi-port device, the corresponding PHY port number is

accessed via the “Port:” pick list shown above the Register Description in Figure 4.

As Figure 4 indicates, the extended MII register pages can be accessed to read or write by clicking on

one of the ExtMII/Ext2MII/ExtGMII tabs.

4.3.1

Board Initialization

Once the evaluation board connectivity has been established and confirmed, the PHY should be

initialized. Initialization can be accomplished by running an init-script sequence, such as performed by

the pre- and post-reset functions of the PHY API standalone app.

While the init-script sequence may not be required for specific operational modes, an init-script

sequence is highly recommended to ensure correct performance over the greatest set of user scenarios

for the PHY. After initialization is performed, refer to the PHY Datasheet section on Configuring the PHY

and PHY Interfaces for the desired application.

An initialization file,

, is included in the GUI package. This initialization file will optimize

vsc8502_init.txt

the copper media interface settings based on the latest factory test result. To execute initialization

script, click “Device” on the top menu and choose “Load Init Script” option, which will automatically load

and execute vsc8502_init.txt file in the directory. Once the initialization is completed, it should say

“LOADED 17 REGISTERS” at the bottom left corner of the GUI Window.

In addition, three other configuration scripts are included:

vsc8502_RGMII_2nsRXCLKdelay.txt: configure the MAC interface to RGMII mode with 2.0 ns RX_CLK

delay compensation. Note that the board is designed and laid out such that the RGMII DATA,

CONTROL and CLOCK for each direction are matched in length approximately /-200 ps.

vsc8502_RGMII_2nsGTXCLKdelay.txt: configure the MAC interface to RGMII mode with 2.0ns